### D2.2

# Architecture models and patterns for safety and security

| Project number:                                                                                 | 644080                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Project acronym:                                                                                | SAFURE                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Project title: SAFety and security by design for interconnected mixed-cr cyber-physical systems |                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Project Start Date:                                                                             | 1st February, 2015                                                                                                                                                                                                                                                                                                                                                                        |  |

| Duration:                                                                                       | 36 months                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Programme:                                                                                      | H2020-ICT-2014-1                                                                                                                                                                                                                                                                                                                                                                          |  |

| Deliverable Type:                                                                               | Report                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Reference Number:                                                                               | ICT-644080-D2.2                                                                                                                                                                                                                                                                                                                                                                           |  |

| Work Package:                                                                                   | WP 2                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Due Date:                                                                                       | Jan 2017 - M24                                                                                                                                                                                                                                                                                                                                                                            |  |

| Actual Submission Date:                                                                         | 31st January, 2017                                                                                                                                                                                                                                                                                                                                                                        |  |

| Responsible Organisation:                                                                       | SSSA                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Editor:                                                                                         | Marco Di Natale                                                                                                                                                                                                                                                                                                                                                                           |  |

| Dissemination Level:                                                                            | PU                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Revision:                                                                                       | 1.0                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Abstract:                                                                                       | This deliverable is a document describing the selection of the modelling languages and tools for the definition of the automotive and telecommunication architectures of interest and the constraints that must be addressed to specify safety and security requirements (including timing constraints) and enable their automatic analysis or the synthesis of mechanisms that guarantee |  |

**Keywords:**

This project has received funding from the European Union Horizon 2020 research and innovation programme under grant agreement No 644080.

the required levels of timing, safety and security.

Modeling, Architecture patterns, MBD, MDA, AUTOSAR, se-

This work is supported (also) by the Swiss State Secretariat for Education, Research and Innovation (SERI) under contract number 15.0025. The opinions expressed and arguments employed herein do not necessarily reflect the official views of the Swiss Government.

curity, safety, time

#### Editor

SSSA

#### Contributors (ordered according to beneficiary numbers)

TEC - Christina Petschnigg, Martin Deutschmann

ESCR - André Osterhues, Lena Steden

MAG - Stefania Botta

SYSG - Mikalai Krasikau, Sergey Tverdyshev

SYM - Jonas Diemer

TUBS - Leonie Ahrendts, Daniel Thiele

SSSA - Cinzia Bernardeschi, Marco Di Natale, Gianluca Dini, Youcheng Sun

#### Disclaimer

The information in this document is provided as is, and no guarantee or warranty is given that the information is fit for any particular purpose. The content of this document reflects only the author's view - the European Commission is not responsible for any use that may be made of the information it contains. The users use the information at their sole risk and liability.

SAFURE D2.2 Page I

#### **Executive Summary**

This deliverable provides the final results of the study on how to model application and platform constraints, metrics and properties that relate in the general sense to safety (including time) and security.

The document provides a summary of the state of the art from scientific research and standardization bodies. Based on the study of the common languages and tools, and the needs of the application context, extracted considering the findings of WP1, the proposals in research papers and other projects, and and the recommendations of standardization bodies, we define an initial set of modeling constructs for time, safety and security.

These constructs are initially represented as abstract, without consideration of an actual language or formalism. Next, they are expressed in UML/SysML and mapped on the AUTOSAR architecture or compatible with the AUTOSAR conceptual framework.

Together with the modeling recommendations, this document provides a description of selected architecture patterns (namely, a separation kernel with possibly a hierarchical scheduler and resource manager and a security encryption module modeled according to the standard requirements) that we expect to be recurrent in the design of mixed-criticality, safety- and security-sensitive embedded systems.

Finally, the report contains a discussion on how to connect the models developed in this work to analysis and synthesis methods and tools and provide a few examples to support the claim on the applicability of the proposed methodology.

SAFURE D2.2 Page II

# Contents

| 1        | Introduction                                                | 1          |

|----------|-------------------------------------------------------------|------------|

|          | 1.1 Safety                                                  | 1          |

|          | 1.2 Time                                                    | 2          |

|          | 1.3 Security                                                | 2          |

|          | 1.4 Definitions and Terms                                   | 3          |

| <b>2</b> | State of the art and Background                             | 5          |

|          | 2.1 Related Projects, Scientific research, Technical papers | 5          |

|          | 2.1.1 Safety                                                | 5          |

|          | 2.1.2 Time                                                  |            |

|          | 2.1.3 Security                                              |            |

|          | 2.2 Standardization bodies and Best practices               |            |

|          | 2.2.1 Safety                                                |            |

|          | 2.2.2 Time                                                  |            |

|          | 2.2.3 Security                                              |            |

| 3        | Guiding principles and Gap Analysis                         | <b>7</b> 5 |

| J        | 3.1 Guiding principles                                      | 75         |

|          | 3.2 Gap analysis                                            | 75         |

|          | 3.2.1 Safety                                                | 75         |

|          | 3.2.2 Time                                                  | 76         |

|          | 3.2.3 Security                                              |            |

|          | 3.2.4 Architecture Features                                 |            |

|          | 0.2.1 Inclinecture remarks                                  | 10         |

| 4        | Abstract Modeling Concepts                                  | 80         |

|          | 4.1 General concepts                                        |            |

|          | 4.2 Safety                                                  |            |

|          | 4.3 Time                                                    |            |

|          | 4.4 Security                                                | 84         |

| 5        | Architecture patterns                                       | 89         |

|          | 5.1 HSM                                                     | 89         |

|          | 5.2 Separation kernel                                       | 90         |

|          | 5.2.1 Overview                                              | 90         |

|          | 5.2.2 Partitions                                            | 90         |

|          | 5.2.3 Services                                              |            |

|          | 5.2.4 Virtualization services on top of separation kernels  |            |

|          | 5.2.5 Modeling                                              | 92         |

| 6        | Concrete Modeling Concepts                                  | 95         |

|          | 6.1 General concepts                                        | 95         |

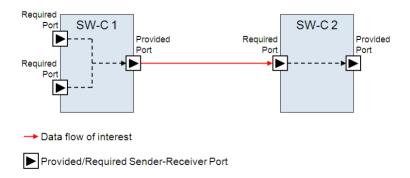

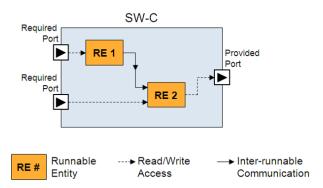

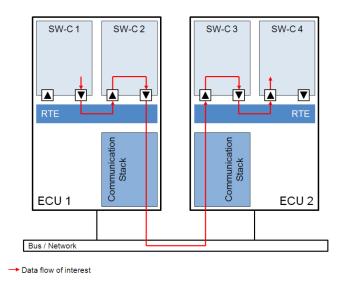

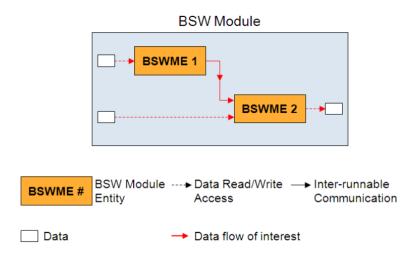

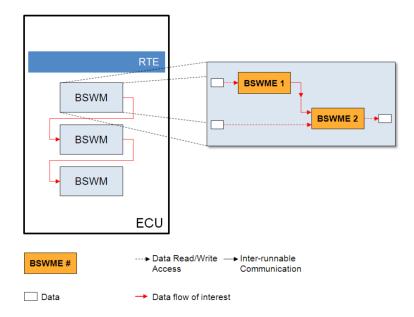

|          | 6.1.1 Input-Output dependencies in AUTOSAR                  | 95         |

|          | 6.1.2 Input-Output dependencies in UML/SysML                | 96         |

|          | 6.2 Time                                                    | 97         |

|          | 6.2.1 Deadline criticality specifications                   | 97         |

|          | 6.2.2 Timing overload specifications                        | 99         |

|          | 6.2.3 Timing execution specifications                       |            |

|          | 0 · · · · · · · · · · · · · · · · · · ·                     |            |

|    |        | 6.2.4 Timing budget specifications                                                      | 100         |

|----|--------|-----------------------------------------------------------------------------------------|-------------|

|    | 6.3    | Security                                                                                | 100         |

|    |        | 6.3.1 Safety                                                                            |             |

|    |        | 6.3.2 Patterns                                                                          |             |

| 7  | Use    | of Modeling Extensions for the Analysis and Synthesis of Safety and Security Properties | 5           |

|    |        | v v i                                                                                   | 109         |

|    | 7.1    | Methodology for Analysis and Synthesis                                                  | 109         |

|    | 7.2    | Analysis of AUTOSAR or UML/SysML models                                                 |             |

|    |        | 7.2.1 Time                                                                              |             |

|    |        | 7.2.2 Safety and Security                                                               |             |

|    | 7.3    | Synthesis of Components and Mechanisms                                                  |             |

|    |        | 7.3.1 Time                                                                              | 121         |

|    |        | 7.3.2 Security                                                                          |             |

| 8  | Sun    | nmary and Conclusions                                                                   | <b>13</b> 3 |

| 9  | List   | of Abbreviations                                                                        | <b>13</b> 4 |

| Bi | ibliog | graphy                                                                                  | <b>13</b> 4 |

# List of Figures

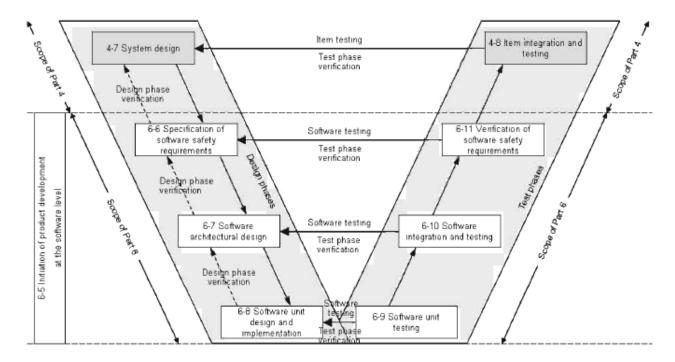

| 2.1  | System development and Safety analyses ([137])                                              | 6  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.2  | SAFE basic system architecture ([137])                                                      | 7  |

| 2.3  | The SAFE metamodel structure and organization ([134])                                       | 8  |

| 2.4  | Safety extensions and packages specified at system and software level ([137])               | 9  |

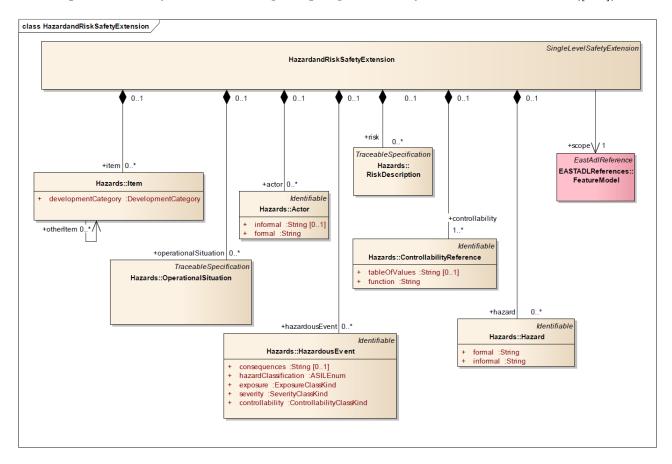

| 2.5  | The SAFE metamodel for hazards and risks ([137])                                            | 9  |

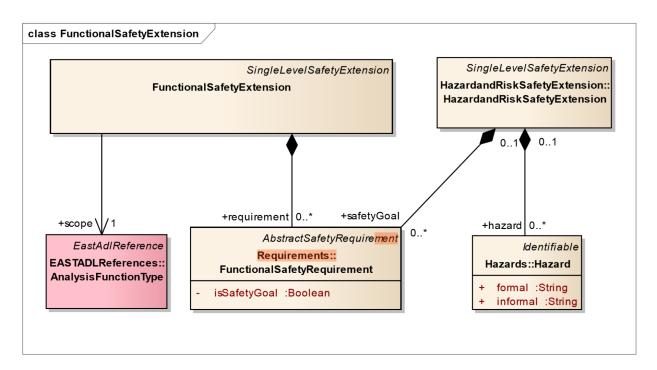

| 2.6  | The SAFE metamodel for Funtional Safety ([137])                                             | 10 |

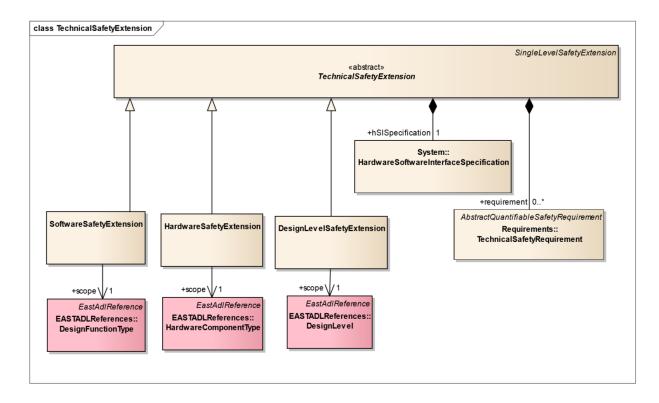

| 2.7  | The SAFE metamodel for Technical Safety ([137])                                             | 11 |

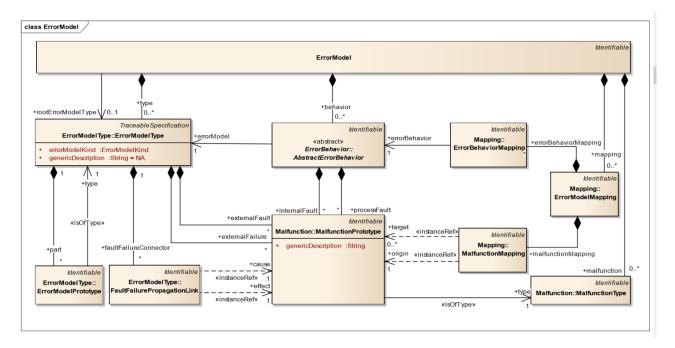

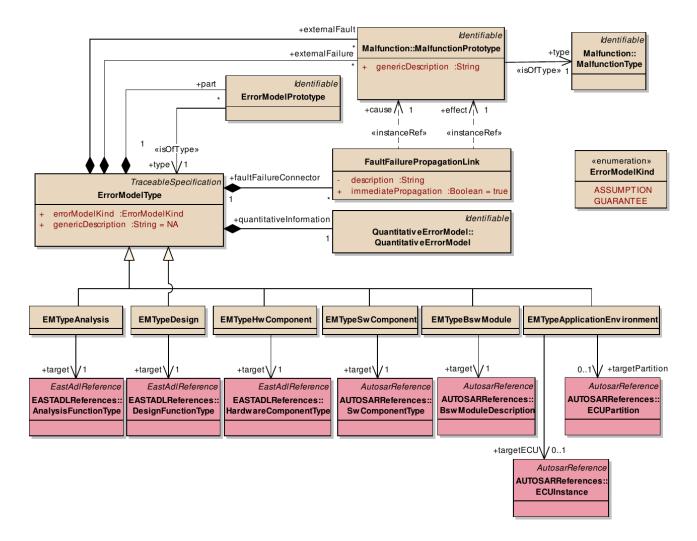

| 2.8  | The SAFE metamodel for the Error model diagram ([137])                                      | 11 |

| 2.9  | Error model prototype ([136])                                                               | 12 |

| 2.10 | Software architecture element ([137])                                                       | 13 |

|      | Integration AUTOSAR element and SW-architecture ([137])                                     |    |

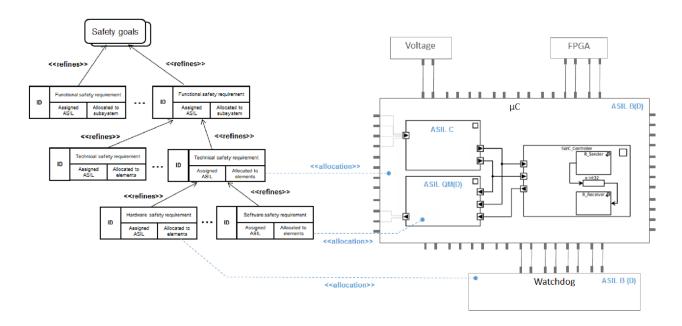

| 2.12 | ASIL allocation to system design elements ([137])                                           | 14 |

| 2.13 | AUTOSAR ECU Resource Overview ([135])                                                       | 15 |

|      | Hardware package overview ([135])                                                           | 15 |

| 2.15 | Hardware Quantitative Measure diagram ([135])                                               | 16 |

| 2.16 | Overview of the safety analysis process ([51])                                              | 17 |

| 2.17 | SAHARA method: Required Resources, Know-How and Threat Criticality ([104])                  | 17 |

| 2.18 | Severity classification scheme ([64])                                                       | 18 |

| 2.19 | Rating of aspects of attack potential ([64])                                                | 19 |

|      | Rating of attack potential ([64])                                                           | 19 |

|      | Classification for Controllability ([64])                                                   |    |

|      | Risk graph ([64])                                                                           |    |

| 2.23 | Organization of Basic TADL2 Elements [147]                                                  | 25 |

| 2.24 | Timing Expression [147]                                                                     | 26 |

|      | The EVITA modeling packages and their relationships                                         | 34 |

| 2.26 | EVITA trust model                                                                           | 34 |

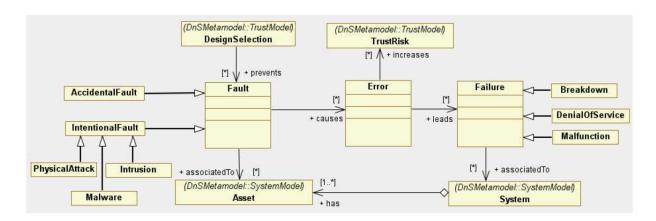

|      | The EVITA model for Faults                                                                  | 35 |

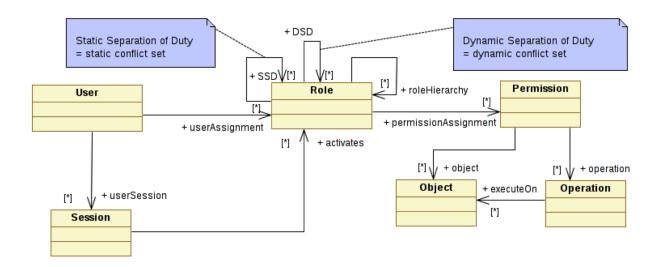

| 2.28 | EVITA modeling of roles and access control policies                                         | 36 |

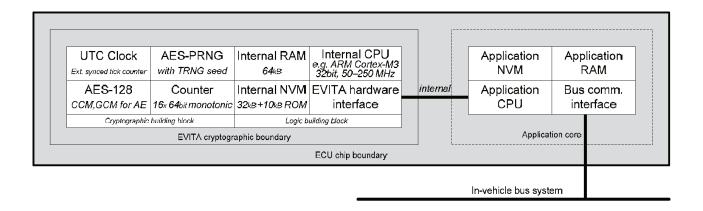

| 2.29 | EVITA full HSM                                                                              | 37 |

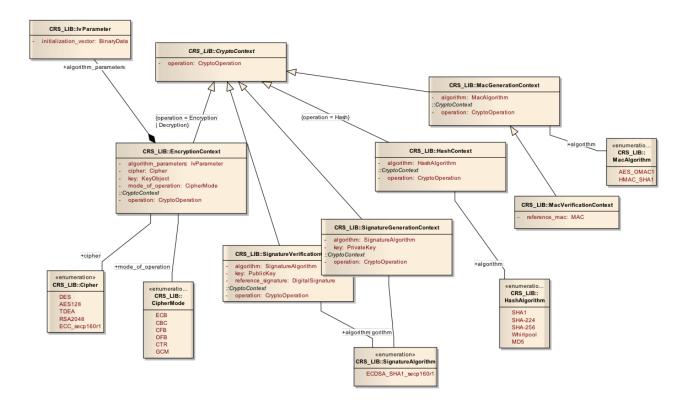

|      | The Evita Cryptographic Services                                                            |    |

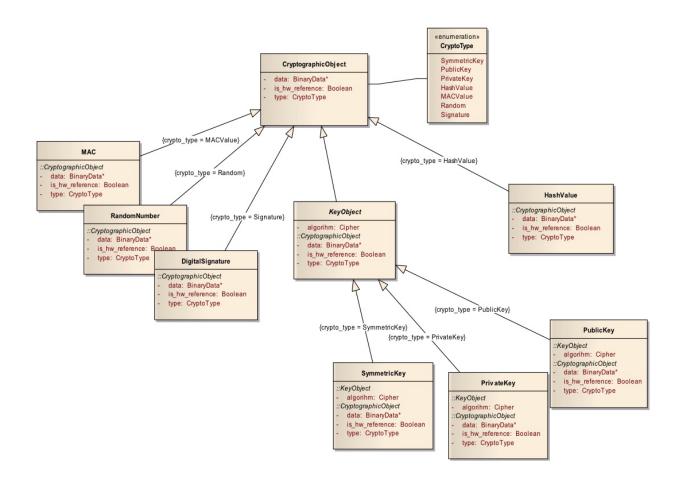

| 2.31 | Cryptographic objects                                                                       | 39 |

| 2.32 | The architecture of an operating system with isolation according to ([4])                   | 40 |

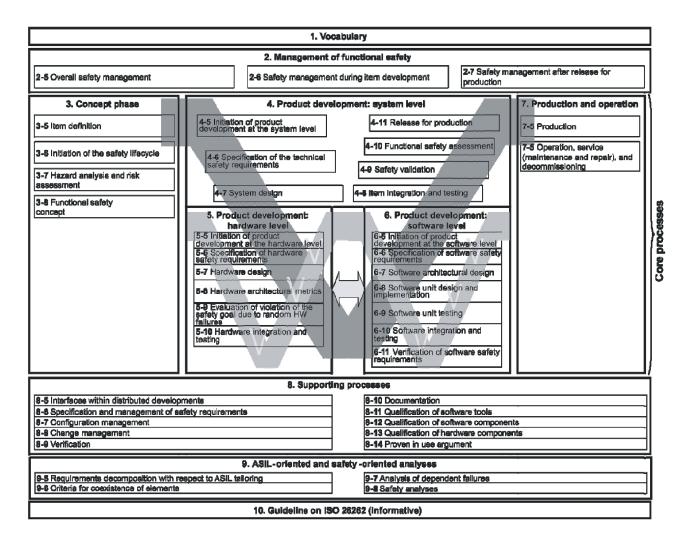

| 2.33 | Overview of ISO 26262                                                                       | 41 |

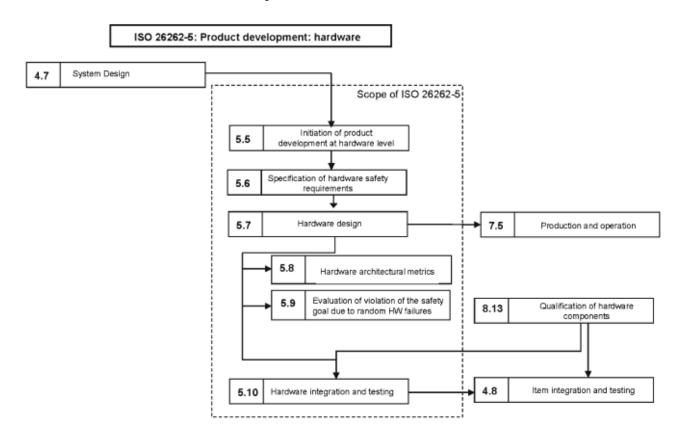

| 2.34 | Reference phase model for the development of a safety related item[83]                      | 43 |

| 2.35 | Reference phase model for the software development [83]                                     | 44 |

| 2.36 | Methods for the verification of the software architectural design [83]                      | 44 |

| 2.37 | Safety requirements metamodel ([24])                                                        | 46 |

| 2.38 | Hierarchy of safety requirements and allocation to system architecture elements ([21])      | 47 |

| 2.39 | Safety measures, safety requirements and allocations to elements of the architecture ([21]) | 47 |

| 2.40 | Scope of the VFB Timing [23]                                                                | 49 |

| 2.41 | Scope of the SW Component Timing [23]                                                       | 49 |

|      | Scope of the System Timing [23]                                                             | 50 |

| 2.43 | Scope of the BSW Module Timing [23]                                                         | 50 |

| 2.44 | Scope of the ECU Timing [23]                                                                | 51 |

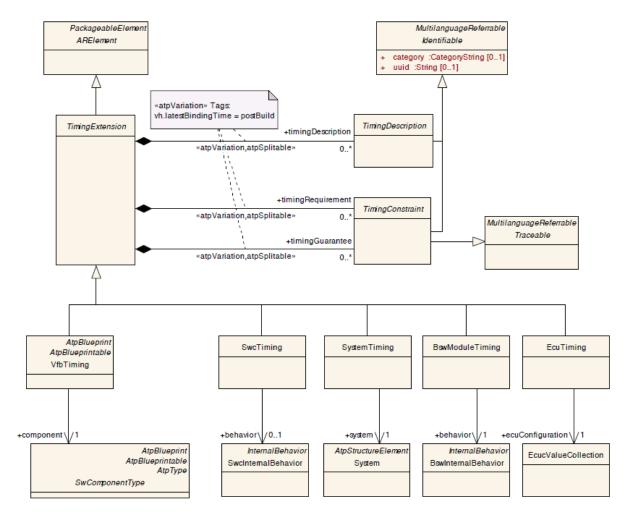

|      | The AUTOSAR framework for timing extensions                                                 | 52 |

| 2.46 | Timing descriptions in AUTOSAR                                                              | 52 |

|      |                                                                                             |    |

SAFURE D2.2 Page V

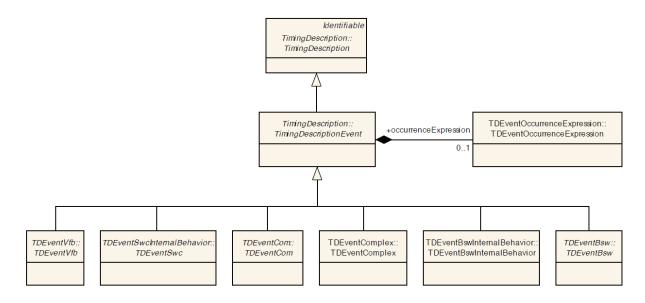

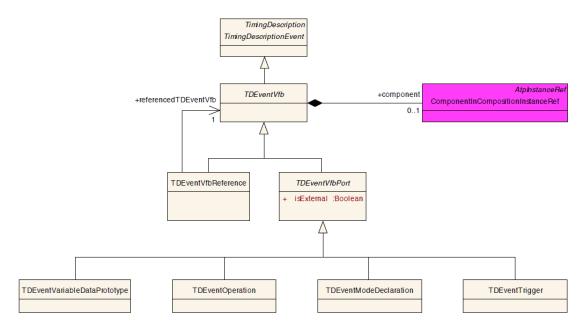

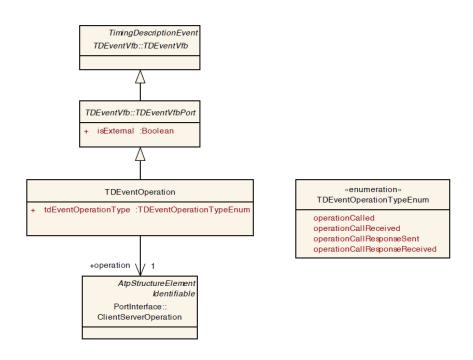

|           | The general classification of timed events                                                      |     |

|-----------|-------------------------------------------------------------------------------------------------|-----|

|           | Timed events applicable to operations                                                           |     |

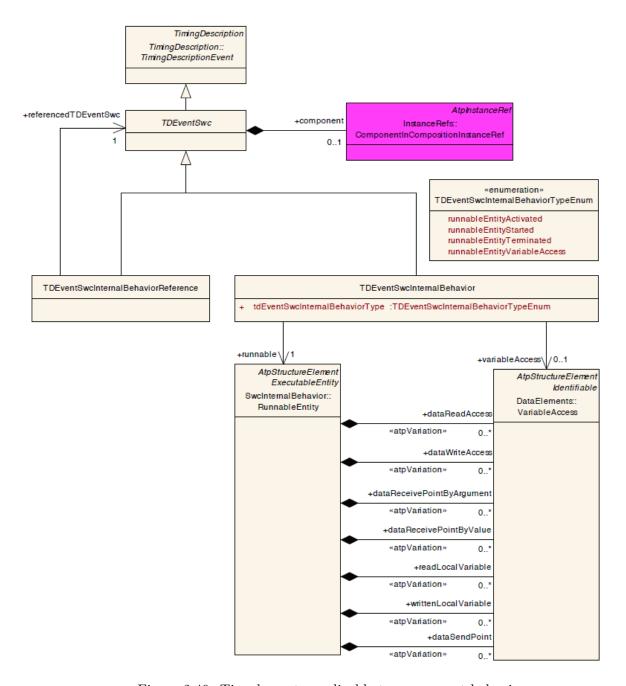

|           | Timed events applicable to component behaviors                                                  | 54  |

|           | Timing descriptions for the definition of event arrivals                                        | 54  |

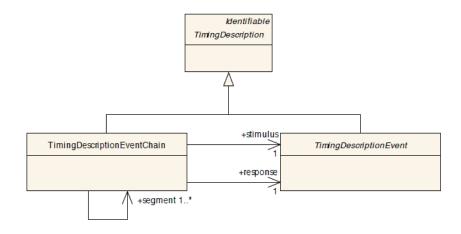

|           | Timing Descriptions for event chains                                                            | 55  |

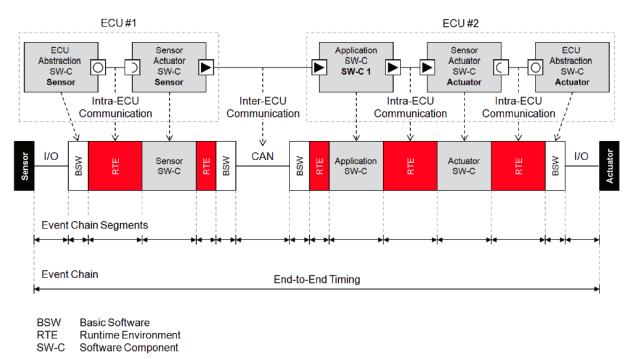

| 2.52      | An example of an end-to-end chain combining execution of computations and transmission of       |     |

|           | messages                                                                                        | 55  |

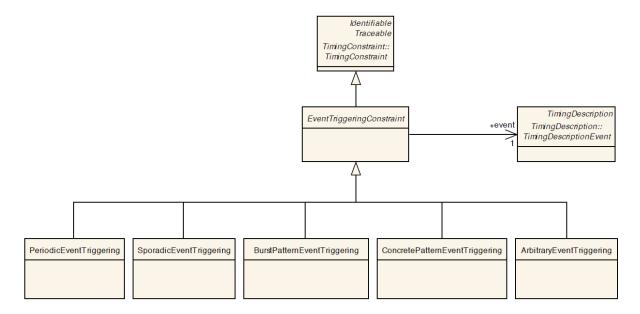

|           | The AUTOSAR entities that are provided for the expression of timing constraints $\dots \dots$ . |     |

|           | Event arrival constraints                                                                       | 56  |

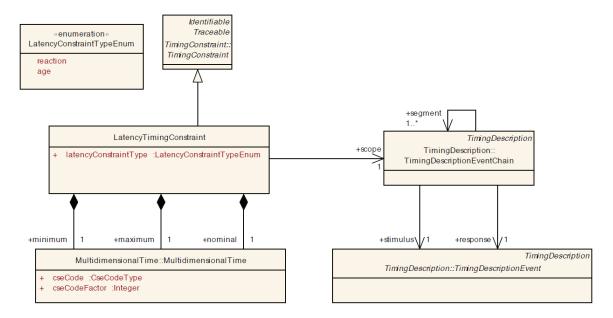

|           | Latency constraints                                                                             |     |

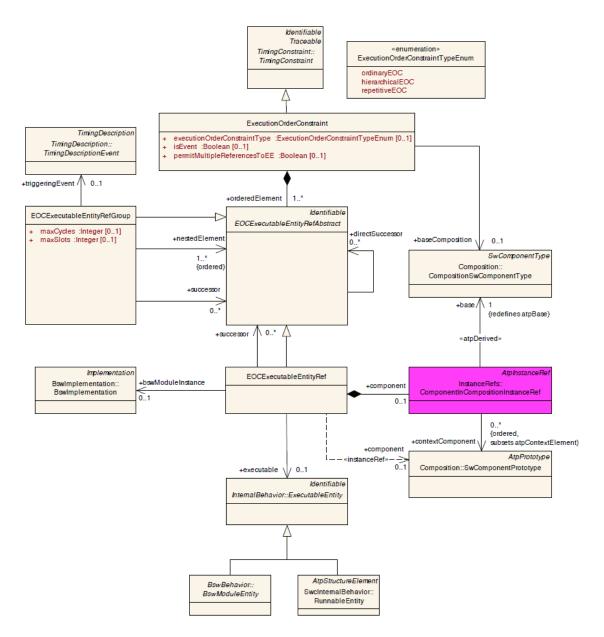

|           | AUTOSAR modeling for the enforcement of an order of execution $\dots \dots \dots \dots \dots$   |     |

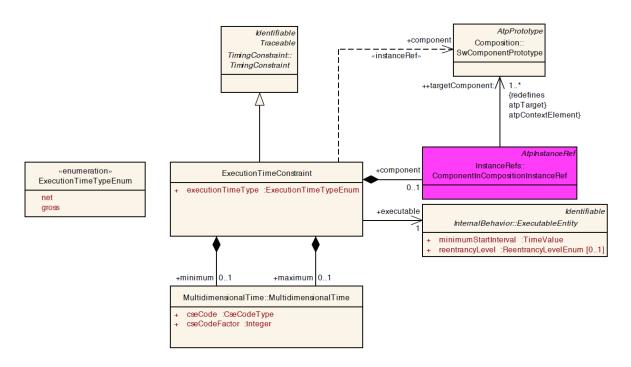

|           | Execution time constraints                                                                      | 59  |

|           | Attributes of an execution time constraint                                                      |     |

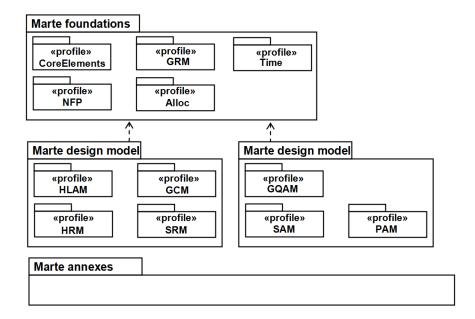

|           | The packages in the MARTE profile                                                               |     |

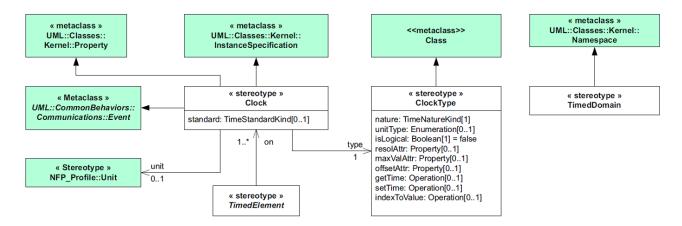

|           | The definition of clocks in the TRM of the MARTE profile                                        |     |

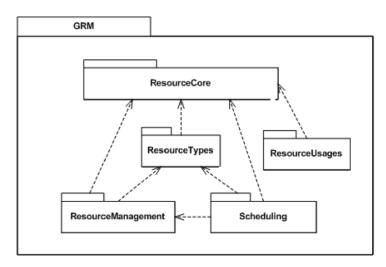

| 2.61      | The main packages for the definition of resources                                               | 63  |

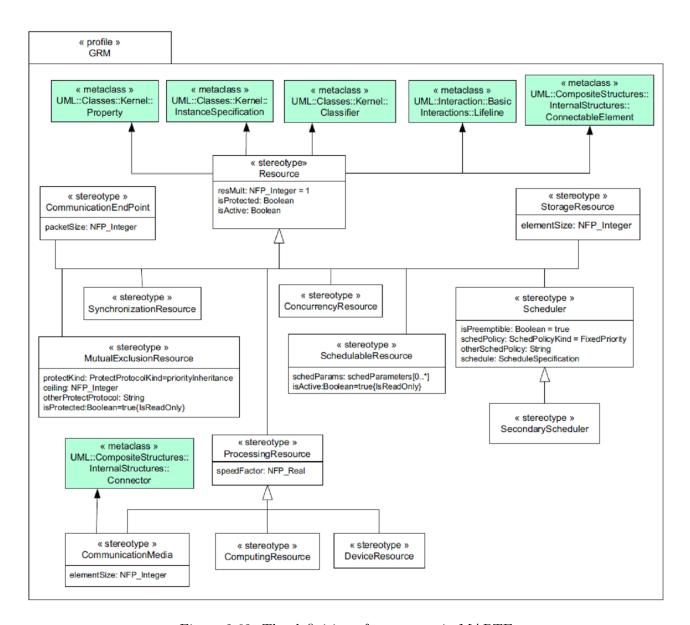

|           | The definition of a resource in MARTE                                                           | 64  |

|           | A schedulability analysis scenario in MARTE                                                     | 65  |

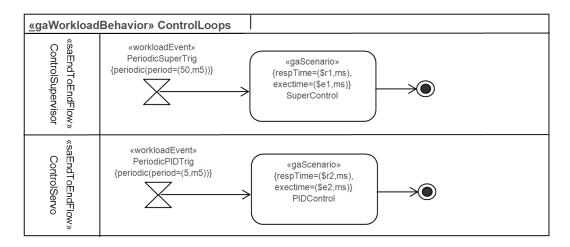

|           | The three domains for security in automotive systems (from [22])                                | 66  |

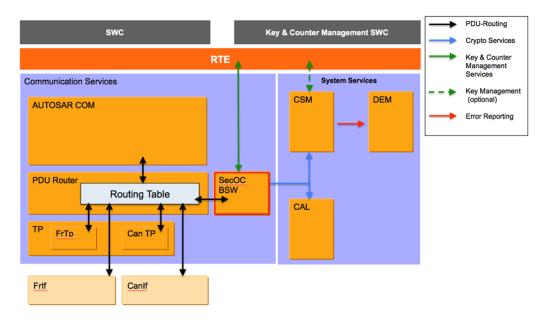

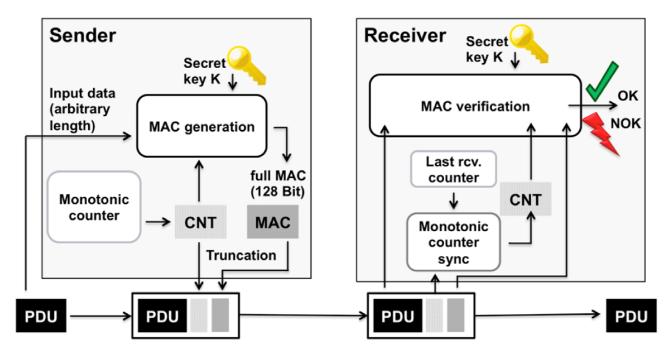

|           | The SecOC component module in AUTOSAR (from [22])                                               | 67  |

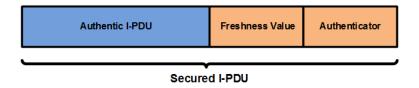

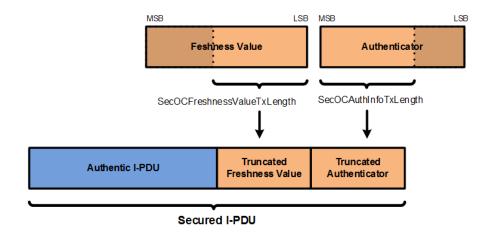

|           | The additional fields in a secure I-PDU (from [22])                                             | 67  |

|           | The security flow (from [22])                                                                   | 68  |

|           | The additional fields in an PDU with truncation options (from [22])                             | 69  |

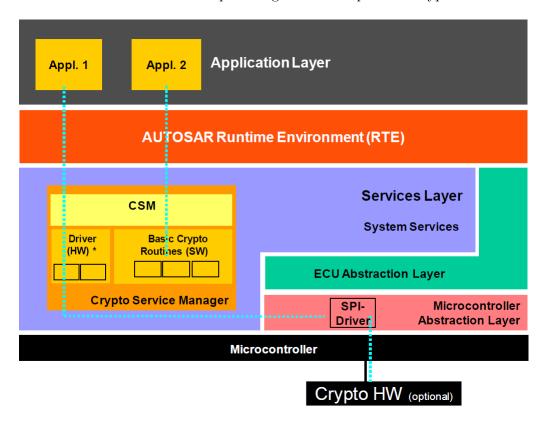

| 2.69      | The architecture-level definition of the CSM module and its relationship with other services in |     |

| o =0      | AUTOSAR (image taken from [20])                                                                 | 70  |

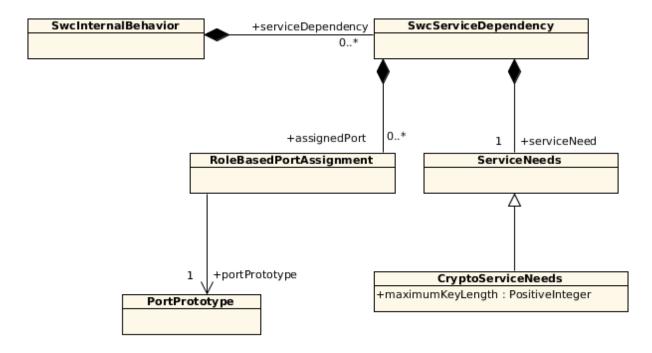

|           | Service dependency meta-model from metamodels in [16]                                           | 72  |

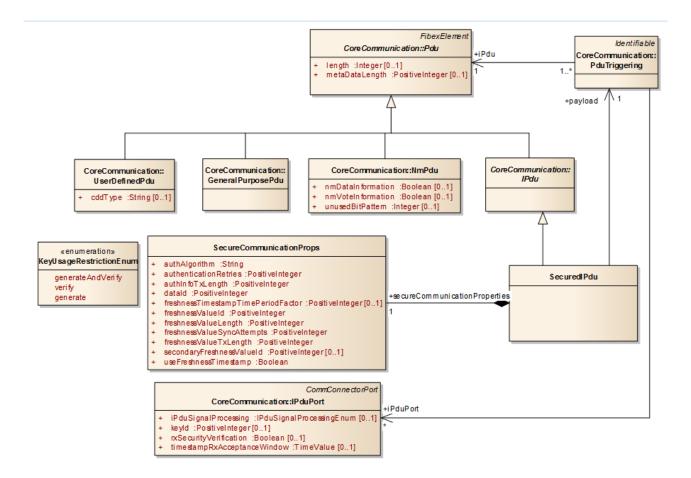

| 2.71      | The security model in AUTOSAR                                                                   | 73  |

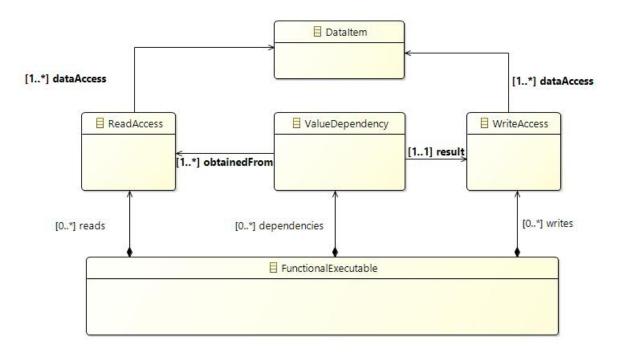

| 4.1       | Expressing dependencies in data processing                                                      | 81  |

| 4.1 $4.2$ | Mapping execution and data                                                                      |     |

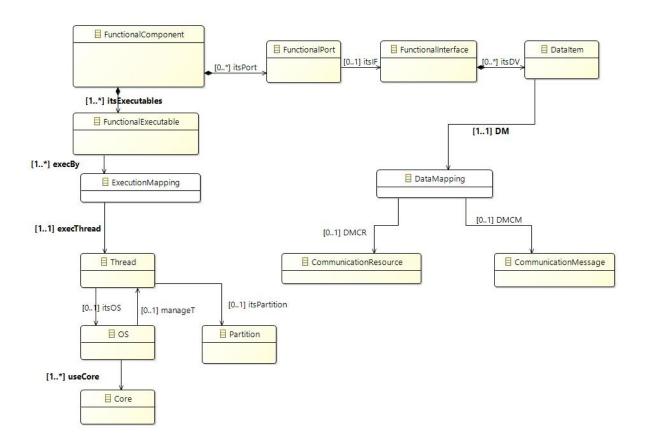

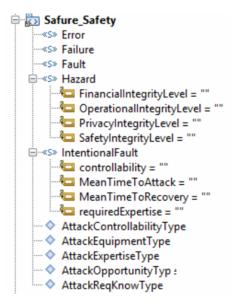

| 4.3       | Metamodel of additional concept connecting attacks to faults and hazards                        |     |

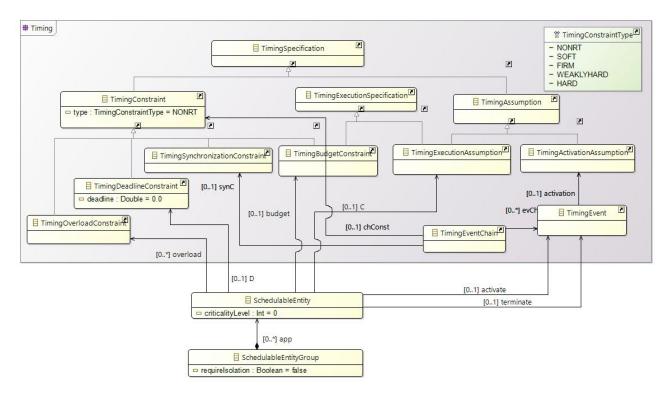

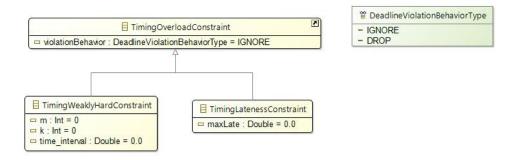

| 4.4       | The modeling concepts for the representation of time constraints and assumptions                |     |

| 4.5       | The modeling concepts for the representation of time constraints and assumptions                |     |

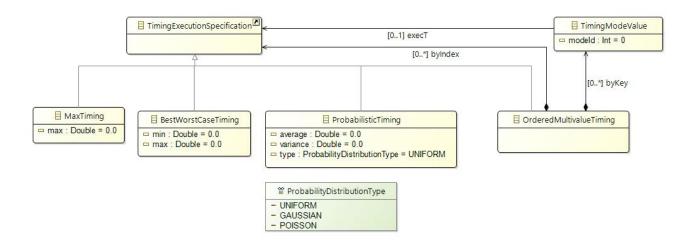

| 4.6       | Specification of execution time assumptions or constraints (budgets)                            |     |

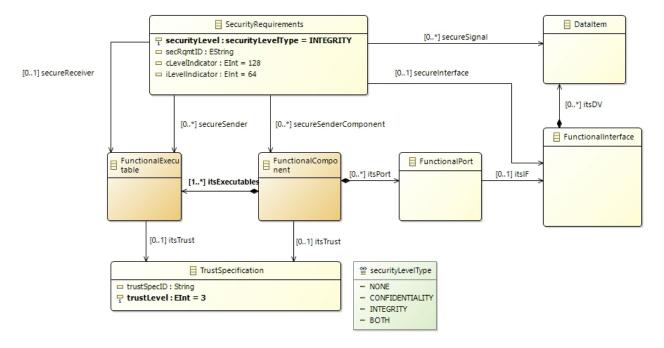

| 4.7       | The modelling concepts for the representation of the functional elements for security           |     |

| 4.8       | The modeling concepts for the representation of secure communication                            |     |

| 1.0       | The modeling concepts for the representation of secure communication                            | 01  |

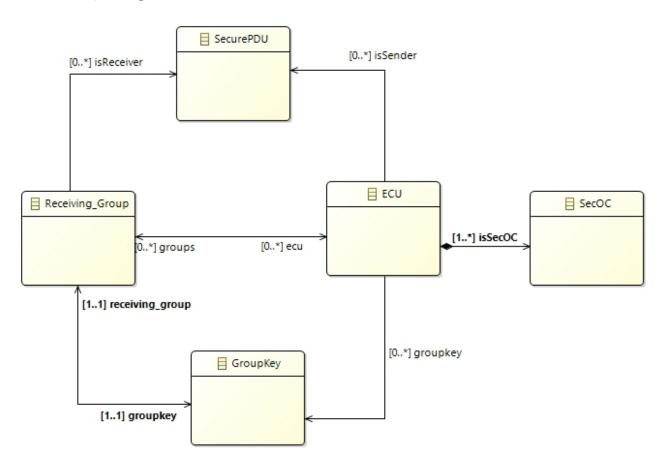

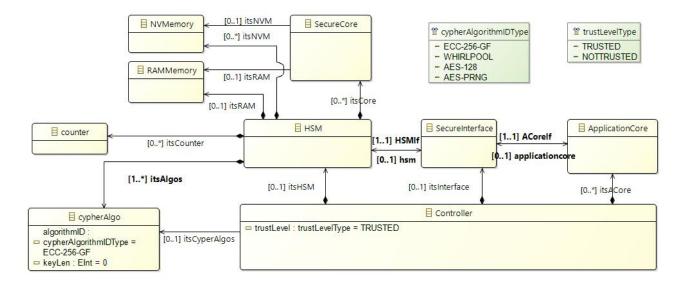

| 5.1       | The modeling concepts for the representation of the platform elements for security              | 89  |

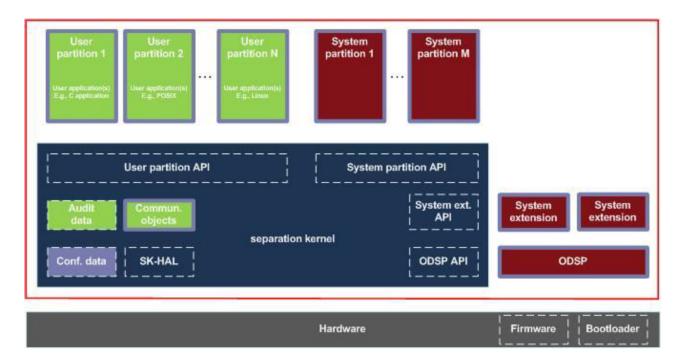

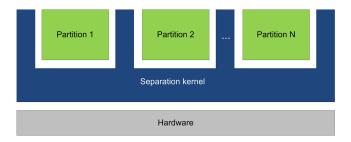

| 5.2       | The generic structure of a separation kernel                                                    | 90  |

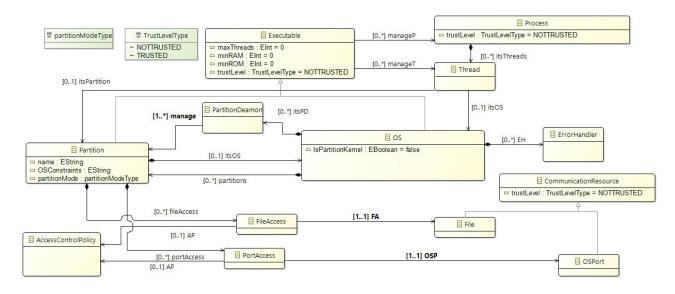

| 5.3       | The modeling concepts for the representation of Hypervisors                                     | 92  |

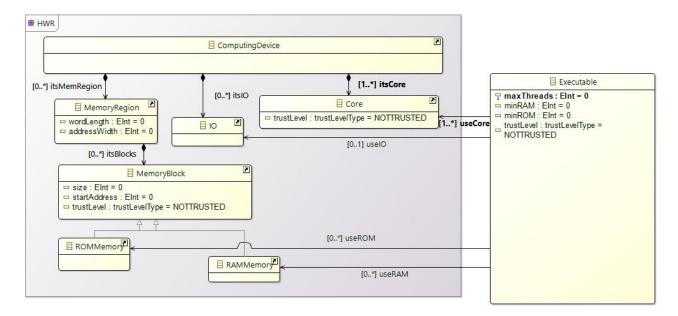

| 5.4       | The modeling concepts for the representation of hardware resources                              | 93  |

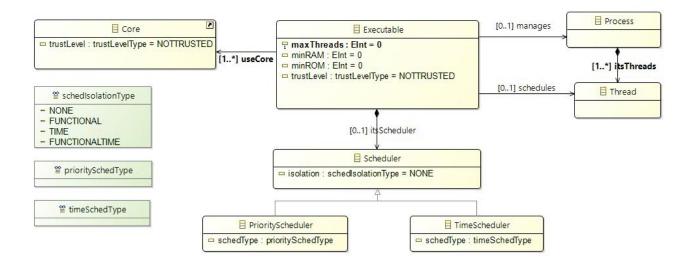

| 5.5       | The modeling concepts for the representation of schedulers                                      | 94  |

|           |                                                                                                 |     |

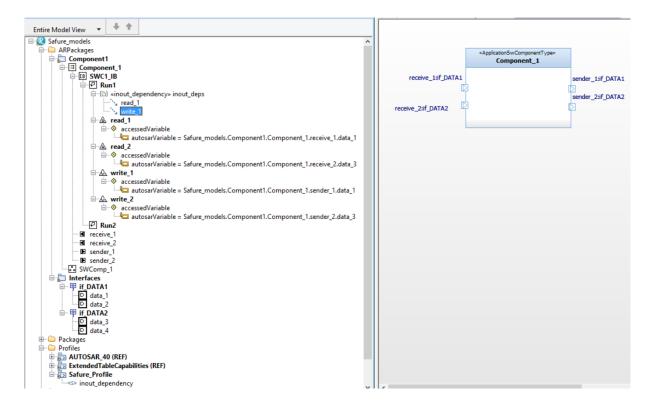

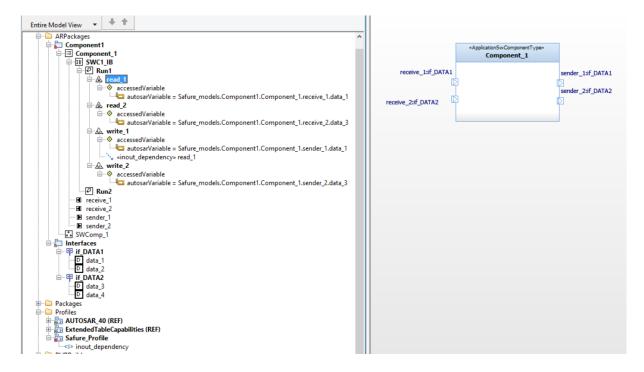

| 6.1       | Expressing dependencies in AUTOSAR-Rhapsody by means of stereotyped constraints                 | 96  |

| 6.2       | Expressing dependencies in AUTOSAR-Rhapsody by means of stereotyped dependencies                | 97  |

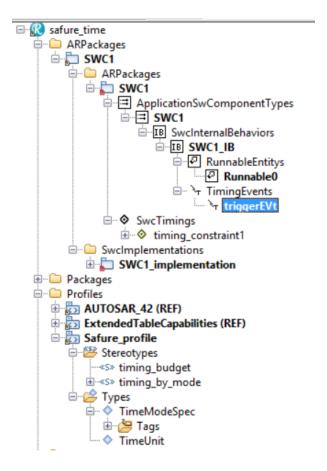

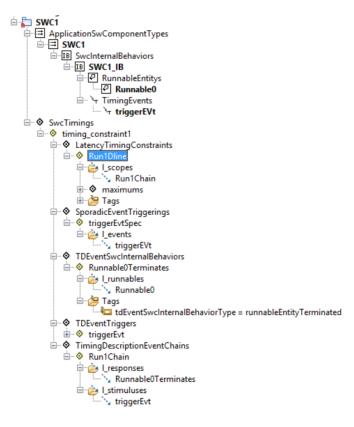

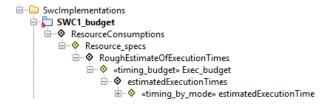

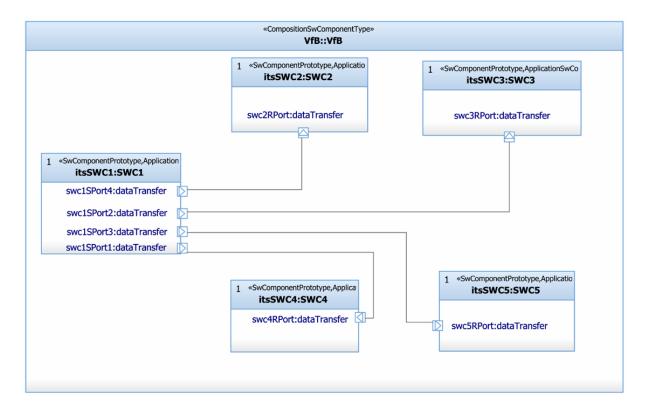

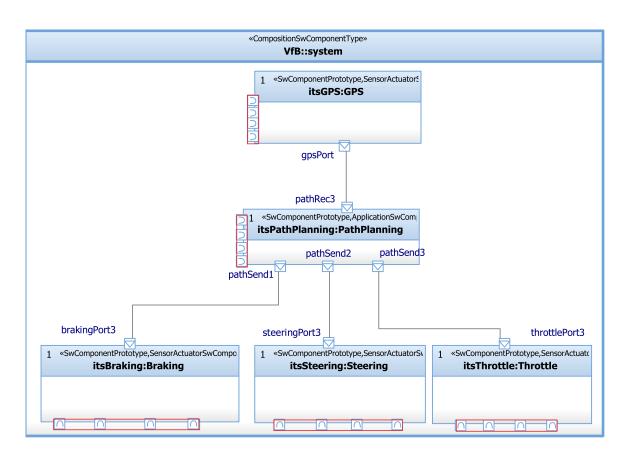

| 6.3       | An AUTOSAR model example to illustrate the implementation of timing extensions                  | 98  |

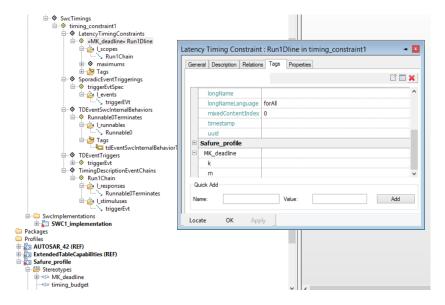

| 6.4       | An AUTOSAR model example with deadline specifications                                           | 98  |

| 6.5       | The definition of types and stereotypes for deadline criticality and missed deadline behavior   | 99  |

| 6.6       | An example with the m-k deadline specification                                                  | 99  |

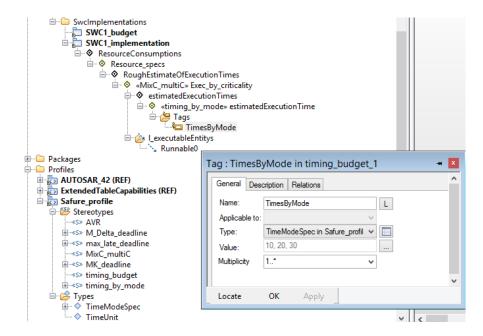

| 6.7       | An example with multiple execution times for a mixed-critical specification                     |     |

| 6.8       | AUTOSAR model example with deadline specification                                               |     |

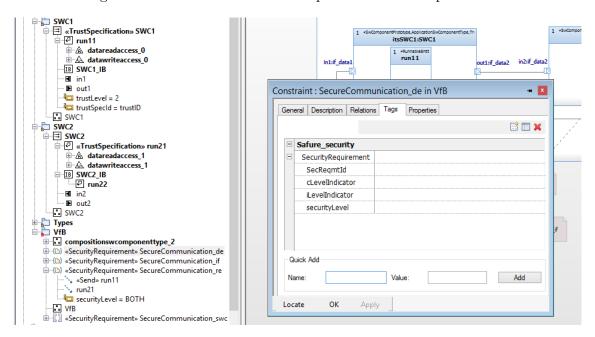

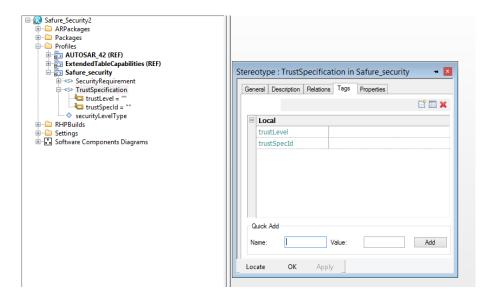

| 6.9       | Definition of a stereotype for security requirements                                            |     |

|           | Definition of a stereotype for trust specifications                                             |     |

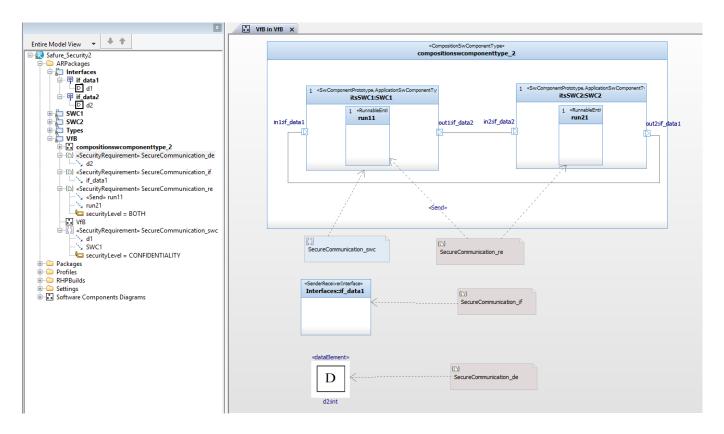

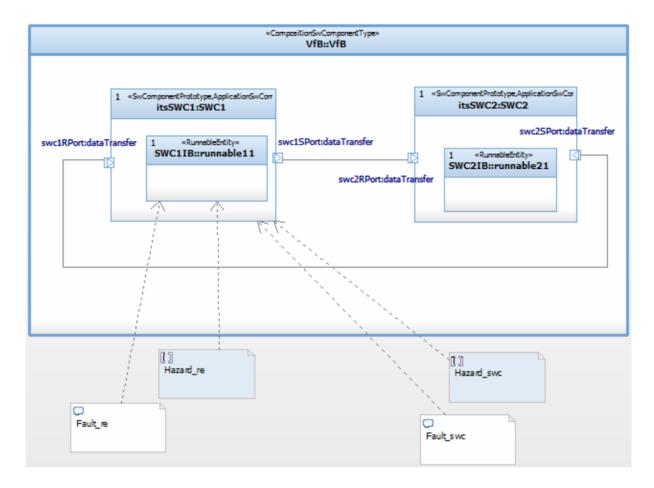

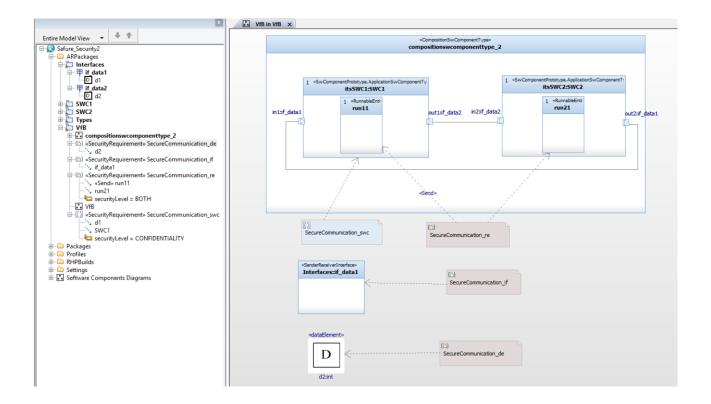

|           | AUTOSAR model with security requirements and constraints                                        |     |

|           | An AUTOSAR example for communication security                                                   |     |

|           | Stereotypes for communication security                                                          |     |

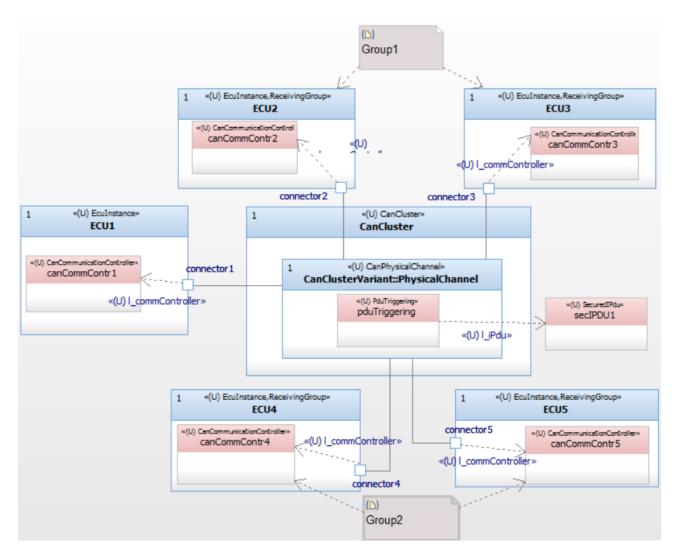

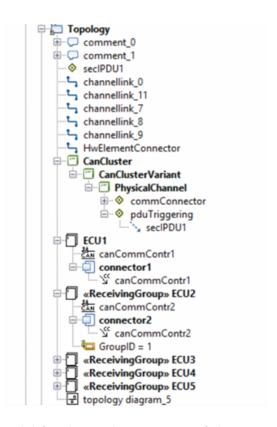

|           | An AUTOSAR example of a communication system with a network configuration                       |     |

|           | The model for the implementiation of the communication system                                   |     |

| 6.16      | Rhapsody stereotypes for intentional faults                                                     | 106 |

SAFURE D2.2 Page VI

| 0.17 | AUTOSAR model with security requirements and constraints                                 |

|------|------------------------------------------------------------------------------------------|

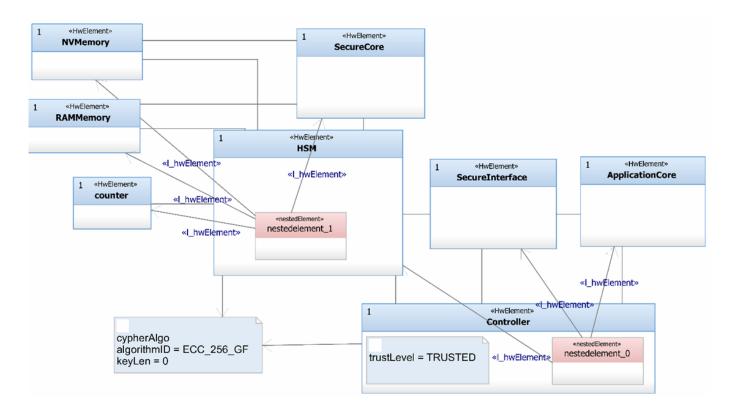

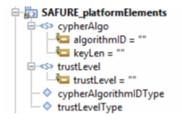

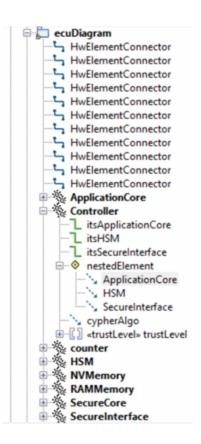

| 6.18 | AUTOSAR model for an HSM pattern                                                         |

|      | Stereotypes for the definition of the HSM pattern                                        |

|      | AUTOSAR model with HSM elements                                                          |

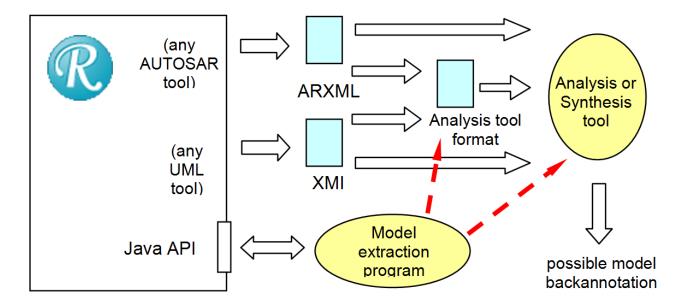

| 7.1  | The general steps and output formats for the analysis of a (AUTOSAR or UML) model or its |

|      | processing for synthesis                                                                 |

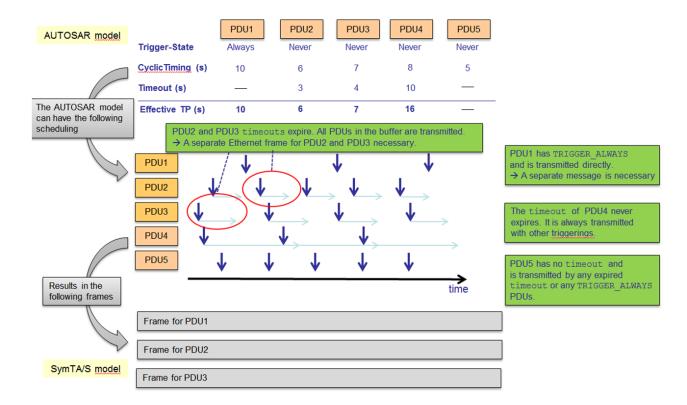

| 7.2  | Example AUTOSAR to SymTA/S Model Transformation                                          |

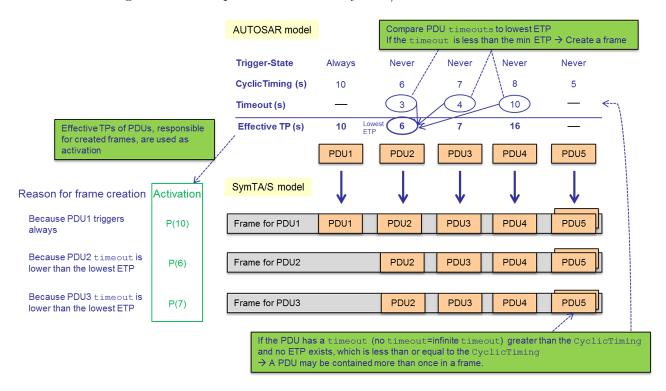

| 7.3  | Model Transformation Effects                                                             |

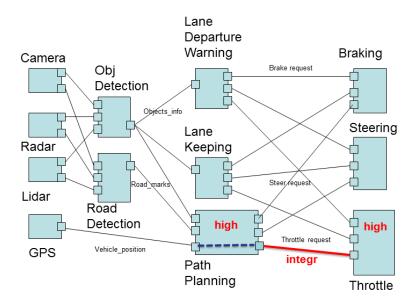

| 7.4  | An example of security annotated model                                                   |

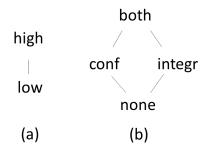

| 7.5  | Order relation on (a) trust levels (b) security requirements                             |

| 7.6  | Algorithm for data security of link $l$                                                  |

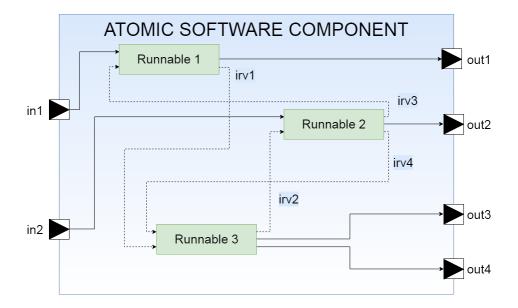

| 7.7  | A software component and its runnables                                                   |

| 7.8  | Code of runnable r1                                                                      |

| 7.9  | Analysis of an AUTOSAR model                                                             |

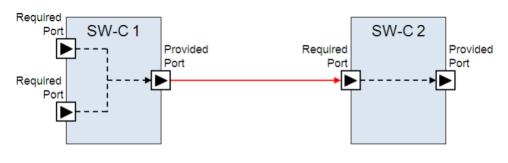

| 7.10 | An example of AUTOSAR port interaction                                                   |

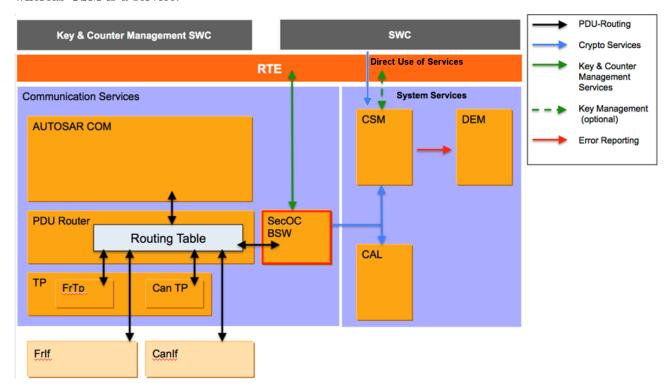

|      | The AUTOSAR standard modules for security                                                |

|      | Example of the CSM function for the initialization of the Mac Generation service         |

|      | An example of use of the Safure extensions                                               |

|      | A sample funtion of CSM library                                                          |

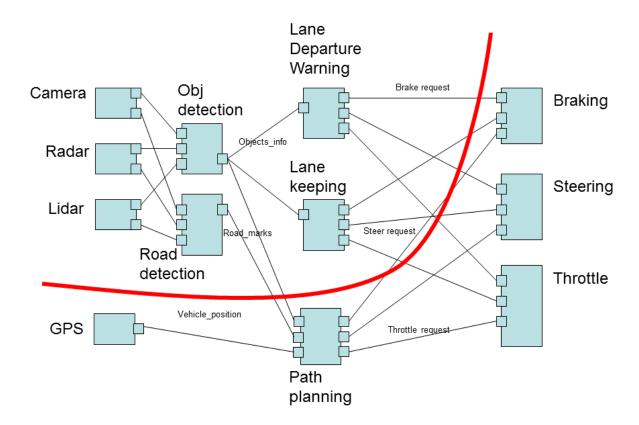

|      | Braking system model overview                                                            |

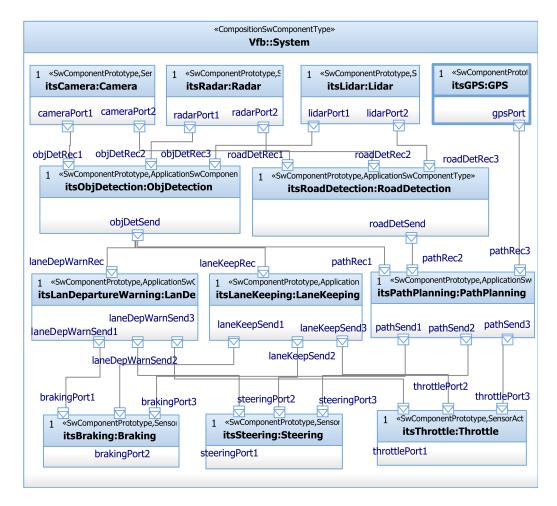

|      | Braking system modeled on IBM Rational Rhapsody                                          |

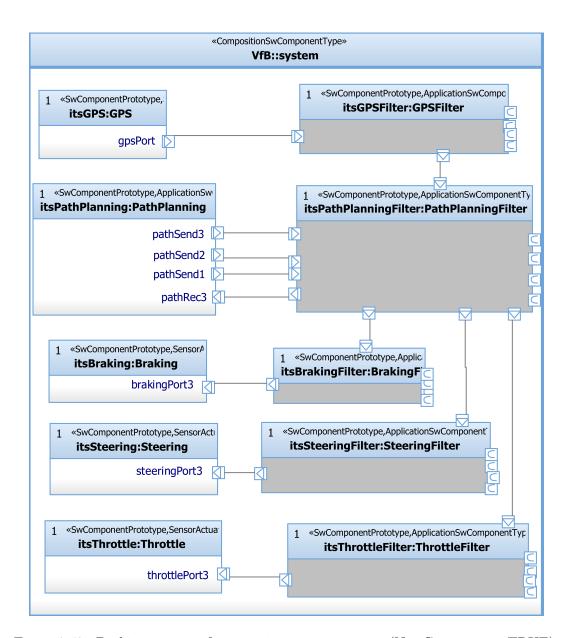

|      | Braking system after security tags processing (NewComponent=TRUE)                        |

|      | Braking system after security tags processing (NewComponent=FALSE)                       |

|      |                                                                                          |

SAFURE D2.2 Page VII

# List of Tables

| 2.1 | Comparing Features of Temporal Logics [37] | 24 |

|-----|--------------------------------------------|----|

| 2.2 | Deadline decomposition approaches          | 27 |

| 2.3 | Security features of the HSM variants      | 37 |

| 7.1 | Initial context file and local memories    | 22 |

| 7.2 | Final context file and local memories      | 23 |

SAFURE D2.2 Page VIII

# Chapter 1

# Introduction

This deliverable is the final result of WP2. It contains the background and analysis results and the presentation of the modeling features that are developed in the WP as an original contribution. In addition, the deliverable describes the possible use of the modeling features presented herein for the purpose of the the analysis and synthesis of safety and security components and mechanisms.

The purpose of this document is to provide a summary of the state of the art documents that are relevant for the objective of the workpackage, that is the definition of modeling features for the description of systems attributes and structure, constraints and properties that apply to the general context of systems with safety (including time) and security constraints. The definition of the modeling features is then made practical by describing the proposed representation of the required modeling concepts in AUTOSAR and UML/SysML.

The scope of the research is potentially huge, spanning across domains that include extremely vast areas of research. To limit the scope and provide meaningful results we restrict the analysis to the domain, the application fields and the case studies of the project. This means that the scope will be limited to embedded systems, with focus on automotive systems and concepts applicable to other CPS domains, including telecommunication. Whenever possible, precedence will be given to the needs of the case studies.

The state of the art analysis has been partitioned along two dimensions: according to the source (academic and technical papers, recommendations of standardization bodies and findings/results of other projects) and according to the domain (Safety, Time and Security). In addition, we strive at identifying the architecture patterns that are needed and/or are most likely going to offer potential for reuse in the systems that are targeted by SAFURE.

Next, based on the findings of the state of the art analysis, we identify the main gaps and needs, the opportunities for reusing or building upon existing standards and results and/or the possibility of providing a concrete definition of concepts that we believe are needed but have been limited to abstract descriptions.

The document structure is the following. Chapter 2 provides the results of the state of the art analysis. Chapter 3 provides a discussion of the guiding principles in the derivation of the modeling recommendations from the results of the state of the art analysis. It also defines the guidelines and the process in the definition of the modeling features and a summary of the analysis of the gaps in existing models and technologies. Chapter 4 contains a (preliminary) description of the abstract modeling concepts that are required. Chapter 5 contains the definition of the architecture patterns for safety and security critical systems.

Finally, Chapter 7 provides examples of concrete implementations of the needed modeling concepts in the modeling languages that are selected as applicable to the domains of interest.

## 1.1 Safety

A safety-critical system is a system whose failure or malfunction may result in death or serious injury to people, loss or serious damage to equipment or environment. Relevant activities in safety-critical systems are:

- Safety requirements identification

- Safety measures definitions

- System safety evaluation

With the increasing complexity of embedded safety-critical control systems, safety is a key issue in automotive system design and development. Safety standards such as ISO 26262 [83] for road vehicles, provide a reference lifecycle to achieve functional safety of E/E systems, based on hazards identification/mitigation and risk analysis.

SAFURE D2.2 Page 1 of 144

The objective of functional safety is to reduce the probability of failures to a given acceptable rate in presence of malfunctioning behaviors. Established techniques for quantitative evaluation of dependability are applied for safety evaluation, like Fault Trees and Failure Mode and Effects Analysis.

Model-based development is a promising approach to handle upcoming issues with modern safety critical systems [103]: it allows to manage the system complexity and several methods and tools for model-based safety analysis have been developed.

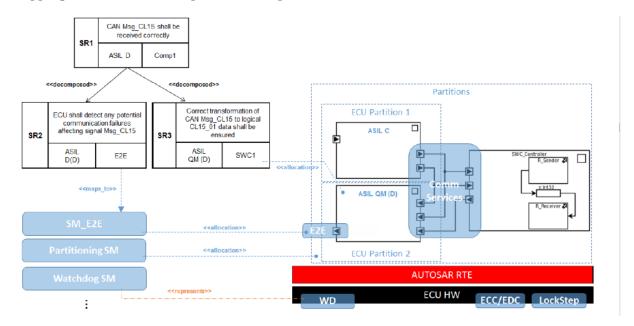

In the automotive domain, the automotive industry adopts AUTOSAR as the reference architecture. Recently, safety extensions have been added in AUTOSAR [21] to develop safety-related sub-systems that comply with ISO 26262, complementing and integrating the specification of safety mechanisms in AUTOSAR. The extensions provide new concepts, including the decomposition of safety requirements, the traceability and the allocation of both safety requirements and safety mechanisms to elements of the system architecture. Traditionally, the concern of safety is with the consequences of failures; however, since security attacks can have catastrophic effects and can lead to violations of safety, security has been recognized as having an impact on safety. Security-aware systematic approaches to evaluate the effects of security issues on system safety are required [91].

#### 1.2 Time

In CPS (Cyber-Physical Systems), a large number of safety constraints require that the system reacts within timing constraints to guarantee a timely reaction to a dangerous condition (such as the anti-lock braking system), or to guarantee that the system goes back into a safe state or simply to ensure stability of the controls that are implemented in the CPS. Given that time requirements play a special role in the general domain of safety constraints and requirements and dedicated models and languages have been dedicated to the specification and analysis of timing properties, they will be discussed in a separate section.

Multiple requirements belong to the general category of modeling languages for the specification and analysis of timing constraints

- specify all the events that pertain to the domain of time and the computation semantics with respect to time (timing semantics and timed events);

- ensure that a computation completes before its deadline (deadline constraints);

- ensure that a timing fault on a selected part of the application will not affect other parts of the application (timing isolation).

Several notable sources of information exist for the definition of timing properties and constraints as well as modeling languages and analysis and synthesis methods, and several conferences are dedicated to research in the domain of real-time systems. Among those, are the Real-time systems symposium (RTSS) and the Real-time and Embedded Application symposium (RTAS) and in general the other conferences that are part of the CPSWEEK. Research on real-time systems can also be found in design automation conferences (like DAC and DATE, that host sessions dedicated to automotive systems). More recently, a new line of research has explicitly targeted *Mixed-critical* systems, with models and analysis algorithms that are aimed at the analysis of systems in which a time- and safety- critical subsystem interacts with other non-safety critical systems by explicit communication or simply by sharing resources.

Among the modeling languages and standards, the AUTOSAR modeling language is especially relevant for automotive systems. Starting from its 4.0 release, AUTOSAR includes a metamodel definition for the specification of some timing features. The UML/SysML language that aims at the definition of a general system-level modeling languages for CPS has been extended for the needs of embedded and real-time systems by the MARTE profile [3]. Other options include other ADLs (Architecture Description Languages) such as EAST-AADL [1]. Finally, many projects have explicitly targeted the definition of timing models and requirements, the analysis of real-time systems and the development of mechanisms for predictable timing behavior. Among those the TIMMO and TIMMO-2 projects provided the groundwork on which the AUTOSAR timing extensions are based [2].

### 1.3 Security

The application of security methodologies and mechanisms to embedded systems follows the general guidelines of security in general purpose computing, with a few differences. In general, security refers to several aspects of systems. With respect to communication, security may refer to the following properties:

SAFURE D2.2 Page 2 of 144

- ensure that a message comes from a trusted sender (authenticity);

- ensure that the information has not been modified on the route from the sender to the receiver (integrity);

- ensure that a message is not a replay (**freshness**);

- ensure that data is not read by an unauthorized entity (confidentiality);

- the sender cannot deny that he is the author/sender/origin of the message (non-repudiation);

- prevent denial-of-service (DoS) attacks from malicious entities that disrupt the communication capabilities (availability).

Authentication and integrity of sensitive data and protection from DoS attacks are necessary to protect correct and safe functionality of vehicle systems by guaranteeing that the received data comes from the right ECU (Electronic Control Unit) and has the correct value. Non-repudiation is usually of lesser importance in embedded systems.

In the context of existing standards (such as the Controller Area Network, CAN), the standard configuration of physical level implementations (the CAN protocol is broadcast and multi-master) offers very limited possibilities for the prevention of DoS attacks and a significant change to the fundamental layers of the communication standard would be required to deal with DoS attacks.

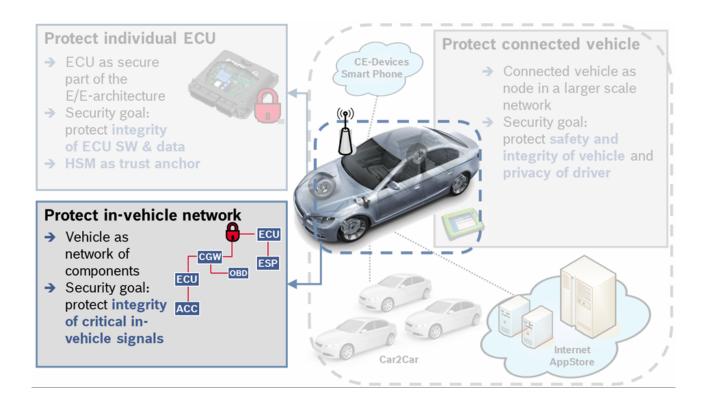

In the automotive domain, the security domains/requirements have been classified according to the architecture hierarchy:

- **Vehicle protection** Refers to the need of protecting the entire vehicle from attacks coming from external connections. The main objective is to protect the safety and integrity of the entire vehicle and the privacy of the driver.

- **Network protection** Refers to the need of protecting the network of components and to guarantee the integrity of communicated signals.

- Node (ECU) protection Refers to the need of protecting the data and state of the functions in execution on an ECU.

#### 1.4 Definitions and Terms

Additional definitions and terms that are used throughout this chapter are listed in this section. A good reference source for security-related definitions is [107].

- ASIL Automotive Safety Integrity Level

- Authentication is a service related to identification. This function applies to both entities and information itself. Two parties entering into a communication should identify each other. Information delivered over a channel should be authenticated as to origin, date of origin, data content, time sent, etc. For these reasons this aspect of cryptography is usually subdivided into two major classes: entity authentication and data origin authentication. Data origin authentication implicitly provides data integrity (because if a message is modified, the source has changed).

- AUTOSAR Automotive Open System Architecture

- ASW Application SoftWare

- BSW Basic SoftWare

- CAL Communications Abstraction Layer.

- **CPS** Cyber-Physical Systems, systems in which a computer system controls, interacts or monitors a physical system.

- CSM Communications Security Module.

- Data integrity is the property whereby data has not been altered in an unauthorized manner since the time it was created, transmitted, or stored by an authorized source. To assure data integrity, one must have the ability to detect data manipulation by unauthorized parties. Data manipulation includes such things as insertion, deletion, and substitution.

SAFURE D2.2 Page 3 of 144

- Data origin authentication is a type of authentication whereby a party is corroborated as the (original) source of specified data created at some (typically unspecified) time in the past. By definition, data origin authentication includes data integrity.

- EAST-ADL Electronics Architecture and Software Technology Architecture Description Language

- EMF Eclipse Modeling Framework

- Entity authentication is the process whereby one party is assured (through acquisition of corroborative evidence) of the identity of a second party involved in a protocol, and that the second has actually participated (i.e., is active at, or immediately prior to, the time the evidence is acquired).

- FAA Function Analysis Architecture

- FDA Function Design Architecture

- **Hazard** A hazard is a potential source of physical injury or damage to the health of persons caused by malfunctioning behavior of the item

- Hazardous Event A hazardous event is a combination of a hazard and an operational situation.

- MAC Message Authentication Code, a portion of a message that is added for the purpose of allowing verification of the message data.

- Message authentication is a term used analogously with data origin authentication. It provides data origin authentication with respect to the original message source (and data integrity, but no uniqueness and timeliness guarantees).

- Operational situation An operational situation is a scenario that can occur during the lifetime of a vehicle.

- PDU Protocol Data Unit.

- RTE Run Time Environment. A layer of software that is automatically generated by AUTOSAR tools to provide the implementation of communication and scheduling in AUTOSAR systems.

- Safety goal A property or condition of a system or subsystem that needs to be asserted in order to guarantee safety.

- Safety relevant failure failures that are identified during safety analyses to have the potential to lead to a violation of a safety goal

- Transaction authentication denotes message authentication augmented to additionally provide uniqueness and timeliness guarantees on data (thus preventing undetectable message replay).

- Unilateral/bilateral authentication: In unilateral authentication, one side proves identity. The requesting side is not even authenticated to the extent of proving that it is allowed to request authentication. In bilateral authentication, the requester is also authenticated at least (see below) to prove the privilege of requesting. There is an efficient and more secure way to authenticate both endpoints, based on the bilateral authentication described above. Along with the authentication (in the second message) requested initially by the receiver (in the first message), the sender also requests an authentication. The receiver sends a third message providing the authentication requested by the sender. This is only three messages (in contrast to four with two unilateral messages).

- WCET Worst Case Execution Time, of the code implementing a function or task executed without interruption on a given CPU considering all the possible states and input values.

SAFURE D2.2 Page 4 of 144

# Chapter 2

# State of the art and Background

This chapter is dedicated to provide a summary of the state of the art with respect to the modeling requirements, languages and standards for safe, secure and time critical systems. The purpose of the state of the art is twofold. On one side, we aim at identifying modeling features (and analysis methods) that have already been defined and/or proposed and can be successfully reused for our needs. Also, we plan to identify commonalities in the approach or the requirements. At the same time we to plan analyze the standards to identify the constraints that apply to our modeling features. The second motivation is to look into proposed analysis methodologies and algorithms and to derive from them the modeling elements that are required to enable them.

The state of the art analysis will be provided in three main sections, the first section focuses on the results that have been published as academic or otherwise technical papers in conference proceedings or journals. This analysis will provide the scientific backbone, by collecting all the established methods and languages, and, at the same time, aims at the definition of the forefront of the research activities in this domain. The second part of the state of the art analysis focuses on the results of other projects, European, international or national, in the same domain as those of Safure. Finally, the third part deals with the analysis of the existing standards, the recommendations for modeling already developed by standardization bodies and the other standard constraints that apply to our modeling definitions.

## 2.1 Related Projects, Scientific research, Technical papers

As for all the other sections, the analysis of the scientific state of the art is divided in the three domains of safety, security and time.

#### **2.1.1** Safety

There is an ever growing interest to implement functional safety in automotive industry to ensure the absence of unacceptable risks in modern cars.

#### SAFE project

The SAFE (Safe Automotive soFtware architecture) project [134] targets the definition and implementation of best practices for the introduction of safety concepts in the automotive domain, with reference to the ISO 26262 [83].

In SAFE, the following objectives are considered:

- Failure error modeling and propagation to perform safety and cut-set analysis.

- Hardware and software COTS evaluation methods for safety test conformity and integration in safety systems

- Clarification of needs via explicit elicitation of safety requirements and tracing

- Specification of criteria and methods for architecture safety evaluation

- Generation of safety case documentation

Several recommendations in SAFE refer to the needs of automatic code generation or are specific of the modeling environment used for the description of the metamodel (and can therefore be made optional). Also, several recommendations are beyond the original scope and can be better characterized as "good modeling practices".

SAFURE D2.2 Page 5 of 144

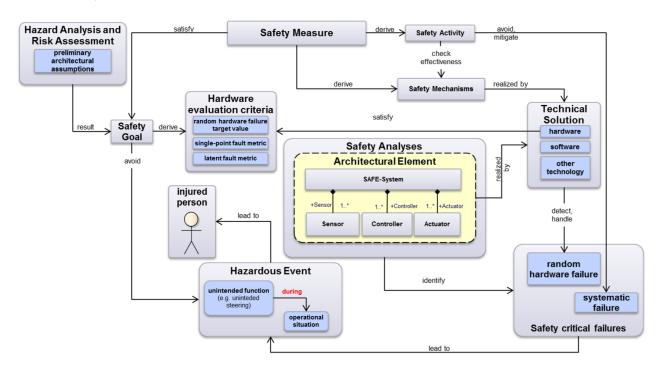

The project spans all the stages in the development cycle, in accordance with a model-based design methodology. Safety analyses are the central topic during the system development to identify safety relevant failures that can cause hazardous events, show implemented safety measures, and prove the effectiveness of the measures (see Figure 2.1). Safety relevant failures (Safety critical failures in the figure) are random hardware failures and systematic failures, typically representing design or coding errors, introduced by the development team. A Hazardous Event (in the figure) is defined as a combination of a hazard with an operational situation. Safety Goals are specified at the vehicle level to avoid the identified hazardous events. An ASIL (Automotive Safety Integrity Level) is assigned to each Safety goal, according to the severity of hazardous events.

Figure 2.1: System development and Safety analyses ([137]).

Central to the ISO 26262 standard, is the concept of Item. In the standard, an Item refers to a specific system or array of systems that implements a function at the vehicle level to which the safety lifecycle is applied. Typically, the function is a safety-related function, with the potential to cause harm to people inside or outside the vehicle. The Item definition is used as input for the execution of hazard analysis and risk assessment.

Based on the information given in the Item and the results of the **Hazard Analysis** and **Risk Assessment** (in the figure), the safety goals are described as functional safety requirements and allocated to architectural elements of the item. Based on the ASIL allocated to the safety goals defined at the vehicle level, a hardware evaluation criterion (in **Hardware evaluation criteria**) for the affected hardware component is selected.

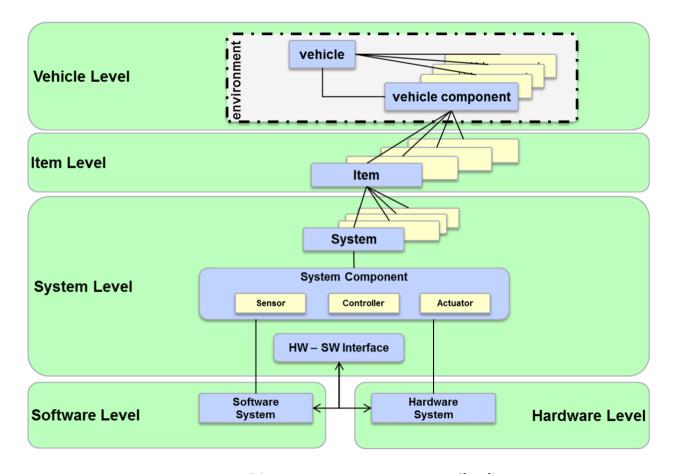

With reference to the SAFE system architecture shown in Figure 2.2, the vehicle level describes the context of the item as well as the architectural splitting up to several Items; the Item level describes the functionality of the item as well as the splitting up to several (sub)systems; the (sub)system level describes the architectural elements of the system. A system consists of components that are in general characterized by having a sensor, a controller and an actuator. The allocations of elements to software and hardware components, and the interfaces between the components are defined within this level; the Software level contains the architectural splitting of a software system to software partitions, software components and units; the Hardware level contains the splitting of the hardware system to hardware components and hardware parts.

The Item level contains different views of the item: the Item Feature view, that identifies all the safety relevant features of the item; the Item Element view, that identifies all the architectural elements that are used for the item; and the Item Failure view, that reports all identified failures caused by architectural elements or development team members.

The Functional Safety concept is among the main features of ISO 26262. The safety concept is initially created during the concept phase and subsequently refined during the product development at the system level. The Functional Safety concept describes the safety measures (Safety Measure in Figure 2.1) that are needed to avoid the violation of the safety goals (i.e., the features to detect and handle safety relevant failures). The Technical Safety concept identifies specific technical solutions to the safety measures identified in the Functional Safety

SAFURE D2.2 Page 6 of 144

Figure 2.2: SAFE basic system architecture ([137]).

concept (Technical solutions in Figure 2.1).

In addition to safety measures, the Functional Safety concept describes fault tolerance mechanisms, and the allocation of the safety measures to the involved architectural elements.

Traceability of safety requirements is supported in SAFE by the concepts of requirement links and requirement allocations. They are both used for refining safety requirements and associating safety requirements with artifacts of the architecture.

In detail, the project targets the following safety-related activities :

- Hazard analysis and risk assessment

- Functional safety concept

- Specification of technical safety requirements, which is further divided into

- Hardware safety requirements

- Software safety requirements

At the end of the conceptual stage (Hazard analysis and risk assessment, Functional safety concept), the SAFE project produced a set of deliverables that define metamodels for the safety-case evaluation and the documentation of vehicle architectures (and/or subsystems).

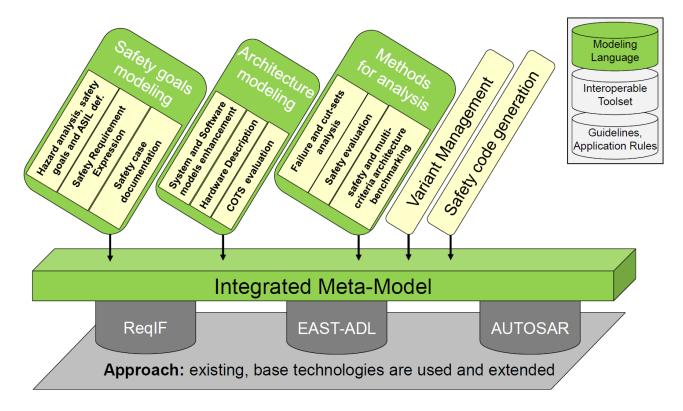

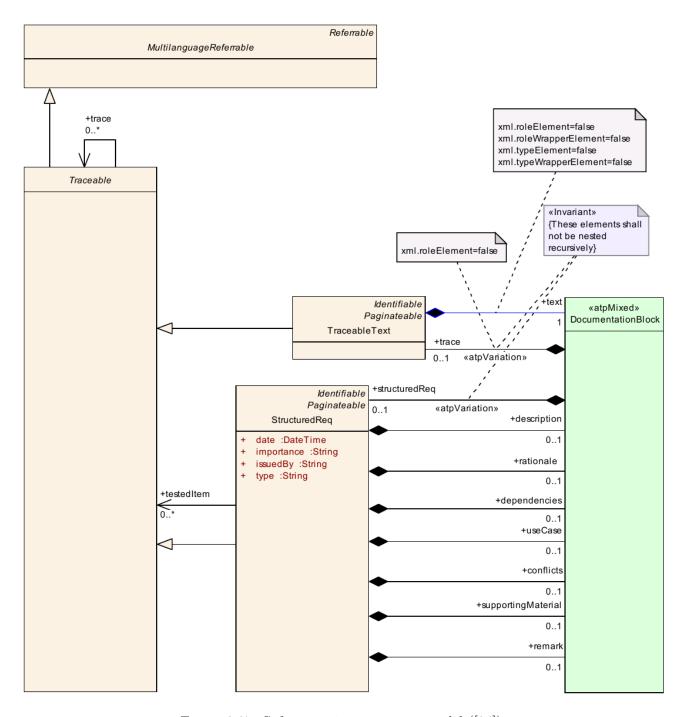

The metamodel produced by the SAFE project is meant to be generic and not tied to any specific language or technology but adaptable to all of them, as shown in Figure 2.3.

The metamodel is based on experience gathered from the automotive domain and other domains, and on existing techniques and modeling languages, such as EAST-ADL for functional abstraction and AUTOSAR for the software component and hardware abstractions. Moreover, the ReqIF format (Requirements Interchange Format) is used for the specification of requirements.

#### The SAFE metamodel.

The SAFE metamodel is structured in the following packages:

SAFURE D2.2 Page 7 of 144

Figure 2.3: The SAFE metamodel structure and organization ([134]).

- CommonStructure: This is a technical package that defines the basic structures

- AUTOSARInstanceRefs.:to enable the referencing of AUTOSAR InstanceRefs from the SAFE metamodel

- DataTypes: for all the types of data

- FormulaExpression: for the definition of a formula language to describe the error propagation

- References: to enable linking and using external metamodels

- SafetyExtensions: for the definition of several abstraction level-specific safety extensions of the SAFE metamodel

- Configuration: containing the definition of elements related to variant management

- ErrorModel: for the description of Basic component failures and the results of safety analysis

- Hardware: for the definition of safety extensions at the hardware level

- Hazards: for the definition of hazard, risk, event, controllability

- Requirements: provides links to a requirements perspective and extends safety elements enabling the requirements traceability that are necessary to fulfil a safety process

- SafetyAnalysis: for the safety analysis that aims at the identification and classification of malfunctions

- Software: for the definition of safety extensions at the software level

- System: for the definition of safety extensions at the system level

In particular, the SAFE metamodel uses elements from foreign metamodels (e.g. EAST-ADL, AUTOSAR), located in the package CommonStrucure/References. The referenced element appears in the SAFE metamodel with the same name as the name in the original metamodel.

#### SAFE metamodel for system and software level modeling.

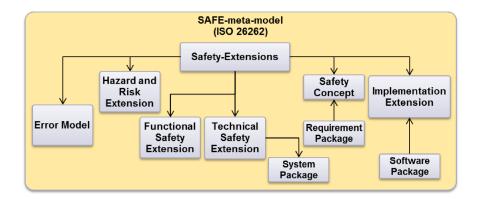

Figure 2.4 summarizes the safety extensions and packages specified for the SAFE metamodel at the system and software level.

SAFURE D2.2 Page 8 of 144

Figure 2.4: Safety extensions and packages specified at system and software level ([137]).

Figure 2.5: The SAFE metamodel for hazards and risks ([137]).

The starting point for the metamodel is the safety-related Item under development according to the definitions of the ISO 26262 framework. The set of modeling concepts is extremely large and will only be summarized here for the portions of interest.

As an example, the SAFE metamodel for hazards and risks modeling is shown in Figure 2.5. The item features are modeled by the feature model that is part of the vehicle level (**FeatureModel** class). The **Hazard** class identifies hazards. The **OperationalSituation** class specifies the operational conditions that include the driver (e.g., gas pedal position), the environment (e.g. nearby obstacles) and other participants (e.g. pedestrians). The **HazardousEvent** class represents an event that is the combination of a hazard with an operational situation. The attributes of the class are consequences, the hazard classification, exposure, controllability and severity. The **RiskDescription** class relates to the risk analysis. The probability of exposure is computed only for operational situations. The classification ranges from Incredible to High probability. The severity classification is taken from ISO 26262.

SAFURE D2.2 Page 9 of 144

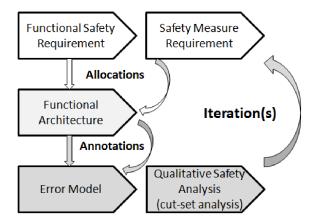

The SAFE metamodel for Functional safety is shown in Figure 2.6. This metamodel specifies the parts that are needed to model the functional safety concept defined in the ISO 26262.

The FunctionalSafetyRequirement class specifies the measures that are needed to avoid the violation of safety goals. In addition, the Functional Safety package describes the safe state for the specified goals, and the allocation of the safety measures to the involved architectural elements. The traceability of the features that causes the failure and the safety measure to handle the failure are part of the functional safety concept.

Figure 2.6: The SAFE metamodel for Funtional Safety ([137]).

The Technical safety metamodel (in Figure 2.7) specifies the safety mechanisms aimed at the detection and control of random hardware failures and at the avoidance or mitigation of systematic failures. The package contains the specification of the technical solution that is put in place to realize the specified safety mechanisms. Technical safety requirements are allocated to architectural elements and ensure traceability. The metamodel specifies the specific technical solutions based on the functional safety concept. It contains the hardware software interface (HW-SW Interface in Figure 2.2) specification (HardwareSoftwareInterfaceSpecification class) and the technical safety concept (TechnicalSafetyRequirements class).

The SAFE metamodel for the Error model is shown in Figure 2.8. The Error model is a container for all the artifacts that are needed to describe the error model of an architectural element: malfunctions, error types and error behaviors. Malfunctions and failures propagate through the complete system model, using the concept of fault failure propagation link (FaultFailurePropagationLink class).

Figure 2.9 shows the **Error model prototype** as specified in SAFE for a concrete function instance. The SAFE metamodel in Figure 2.4 includes the packages:

#### • System Package

contains the extensions that are needed to cover a safety architecture at the system level. In addition to the Functional safety extensions and the Technical safety extensions, the package contains the Safety measures and mechanisms to avoid, mitigate, detect or control safety relevant failures.

#### • Software package

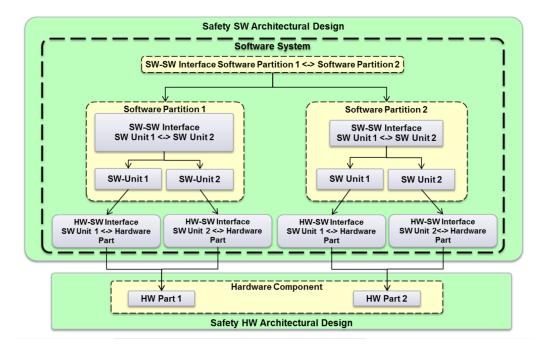

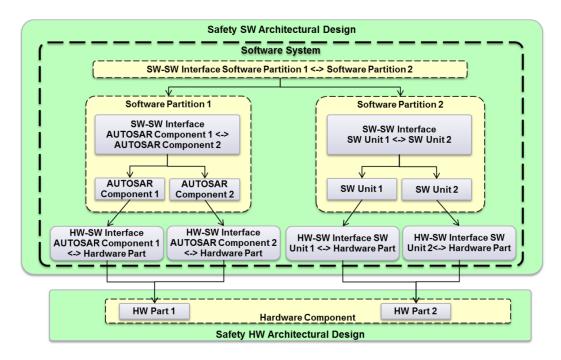

contains the elements for the definition of the safety architecture at the software level. The schema for a generic safety relevant architecture element at the software level is shown in Figure 2.10. In particular, software safety requirements are derived from the technical safety requirements and are drive the software development. Software partitions are identified to satisfy the independence of safety requirements. SW partitions (Software Partition 1, Software Partition 2) are designed with sufficient independence to ensure that a software feature realized in one partition cannot compromise a software safety requirement defined for any other software partition.

SAFURE D2.2 Page 10 of 144

Figure 2.7: The SAFE metamodel for Technical Safety ([137]).

Figure 2.8: The SAFE metamodel for the Error model diagram ([137]).

In addition, software safety mechanisms are allocated to the architectural elements at the software level. Software verification is planned following the activities of software unit testing, software integration and testing, verification of software requirements, verification of calibration/configuration data, and others. AUTOSAR elements are integrated into the software architecture as shown in Figure 2.11 in which the AUTOSAR modeling entities appear in place of the generic concepts of Figure 2.10. Before the integration of the software components, each AUTOSAR SW-Component must qualified to provide evidence for its safe use.

SAFURE D2.2 Page 11 of 144

Figure 2.9: Error model prototype ([136]).

### • Requirement Package

contains the categorization of safety requirements into groups: Functional Safety Requirements, Technical Safety Requirements, Software Safety Requirements and Hardware Safety Requirements. Moreover, each safety requirement is assigned a sub-category that specifies the use case of the requirement (e.g, the sub-category *Process* means that the requirement describes safety relevant verification methods; and the sub-category *Product* means that the requirement specifies the technical solution to fulfil safety goals).

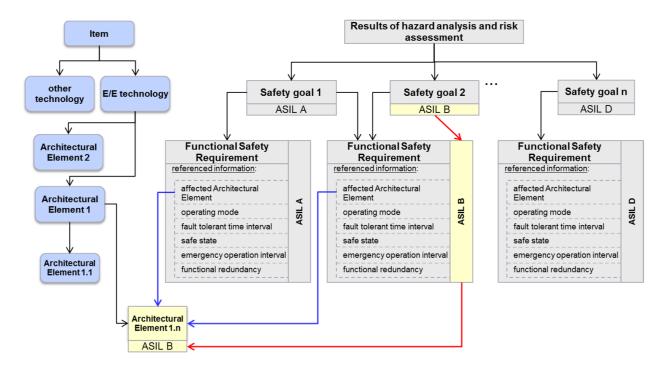

Safety goals are evaluated and classified according to ASILs. In the assignment of the ASIL level, three parameters are considered: exposure (how often people involved may be put at risk), controllability (how well the individuals involved can handle the problem) and severity (seriousness of the consequences). Safety goals are implemented in accordance with the classified ASIL, and each system design element inherits the highest ASIL from the technical safety requirements that specify mechanisms realized in the elements, as shown in Figure 2.12. If an element of an AUTOSAR specification is characterized by an ASIL level, the element is in the scope of an ISO 26262 development.

#### SAFE metamodel for Hardware modeling.

At the HW architectural level, hardware subsystems and components are split down to the level of the hardware elementary elements.

The basic steps in the hardware modeling are [135]:

- Capture the Hardware Technical Safety Concept;

- Complete the HW Component Failure Propagation on the Hardware Architecture;

SAFURE D2.2 Page 12 of 144

Figure 2.10: Software architecture element ([137]).

Figure 2.11: Integration AUTOSAR element and SW-architecture ([137]).

- Define the target values for all the HW Components and calculate the corresponding metrics;

- Define the Hardware Part Allocation and Malfunction;

- Develop the Electronics Schematic (by capturing all electronic Hardware Parts as Hardware Elements in AUTOSAR);

- Perform the Electronic FMEA and evaluate its contribution to the HW Component malfunctions;

- Verify the Component Metrics and the Probabilistic values.

In particular, in the Failure propagation on hardware architecture step, the following activities are executed:

SAFURE D2.2 Page 13 of 144

Figure 2.12: ASIL allocation to system design elements ([137]).

- 1) classify the character of the failure and the contribution of each fault by using the cut-set order and the coverage of a safety requirement with the specification of the diagnostic coverage of each safety mechanism;

- 2) tag each failure as Single Point, Residual, or Multiple Point Latent;

- 3) Identify the primary Hardware Safety Requirements based on the top-level malfunctions of the HW Architecture. The primary Hardware Safety Requirements shall prevent the occurrence of the malfunctions of the Hardware Components.

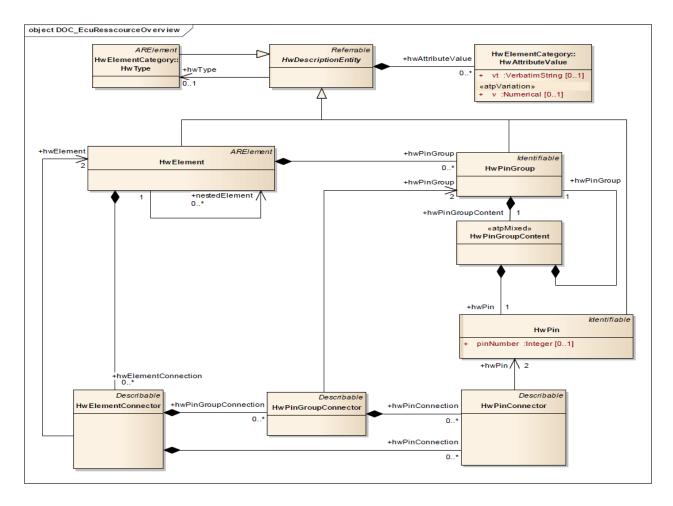

In AUTOSAR, the ECU Resource Template contains the elements to represent the hardware-related part of the system, as shown in Figure 2.13. An ECU is defined as a nested **HwElement**, connected by their **HwPins**, and **HwPinGroups**, to represent all **Hardware Parts** and to define a complete ECU electronic schematic at the hardware electronic design level.

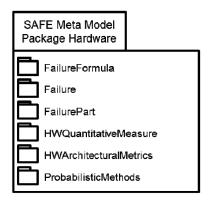

The Hardware Package defines the extensions for the hardware part, as represented in Figure 2.14. It consists of the following sub-packages:

- FailureFormula contains all the equations that are necessary for the evaluation of the hardware architecture

- Failure describes the failure mode of the hardware component

- FailurePart describes the failure mode of each hardware part

- HWQuantitativeMeasure for the definition of the required quantitative safety analyses

- HWArchitectureMetrics for the calculation of hardware architectural metrics

- ProbabilisticMethods for the description of the residual risk of each safety goal due to random hardware failures. This package contains the definition of probabilistic metrics for random hardware failures (PMHF) and failure rate class methods (FRC).

SAFURE D2.2 Page 14 of 144

Figure 2.13: AUTOSAR ECU Resource Overview ([135]).

Figure 2.14: Hardware package overview ([135]).

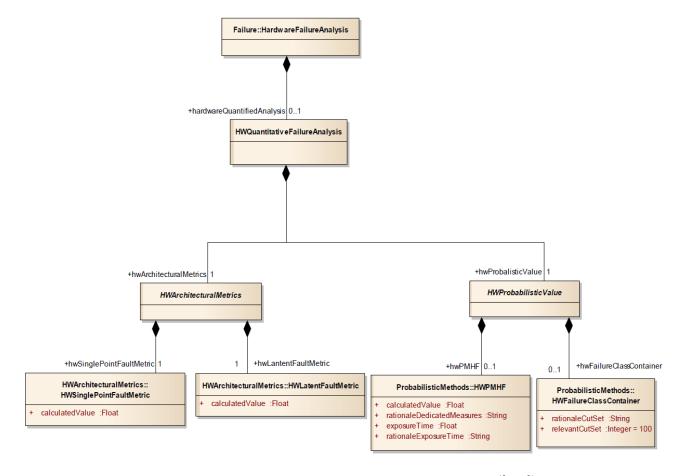

As an example, Figure 2.15 shows the diagram for the **HWQuantitativeMeasure** package, which gives an overview about the quantitative analyses.

Given a Safety goal, the class **HWQuantitativeFailureAnalysis** represents the container for all the quantified failure analysis methods (**HWArchitecturalMetrics** class and **HWProbabilisticValue** class).

The HWArchitecturalMetrics class collects the hardware architectural metrics: the single-point fault metric, that describes the robustness of the hardware architecture to cope with single-point and residual fault (HWS-inglePointFaultMetric class), and the latent fault metric, that describes the robustness of the hardware architecture to cope with multiple-point latent faults (HWLatentFaultMetric class).

**HWProbabilisticValue** is the class for storing the results of one of the two probabilistic methods: Probabilistic Metric for random Hardware Failures (**HWPMHF** class) or Failure Rate Class ( **HWfailureClassContainer**

SAFURE D2.2 Page 15 of 144

Figure 2.15: Hardware Quantitative Measure diagram ([135]).

class).

The attribute calculated Value of the **HWPMHF** class is the result of the calculation of the PMHF. The attribute rationale Dedicated Measures shall allow defining a rationale for the dedicated measures applied to the design. The exposure Time attribute is the duration of the exposure used in the simplified computation of the PMH. The attribute rationale Exposure Time is for the Documentation of the rationale for the definition of the Exposure Time.

The HWfailureClassContainer class stores all the hardware element failure class results and the associated assumptions for the saving of the cut-set cut context as recorded in its attributes. The attribute rationaleCutSet provides a textual rationale for the number of relevant cut-sets and relevantCutSet stores the number of relevant cut-sets.

#### Threats and risk analysis

Safety-critical systems are vulnerable also to security threats. The identification of security threats as faults appeared as early as in 2004 in the paper by Avizienis et al. [29]. This paper represents the result of an effort to bring together the common strands of dependability and security. In the paper, faults are classified according to viewpoints: one of the viewpoints distinguishes between **nonmalicious** and **malicious faults** (faults introduced with the objective to cause harm to the system). Malicious faults are grouped into two classes: **Malicious logic faults** that encompass development faults and **Intrusion attempts** that are operational external faults. As new functionalities and technologies are introduced in automotive industry, a security-aware safety development process has become a crucial factor. In [104], the authors present an approach to safety evaluation that is a combination of the automotive hazard analysis and risk assessment (HARA) with the STRIDE approach typical of the security domain (a threat modeling approach that uses six security threat categories to review system design). During the hazard analysis and risk assessment (HARA), the evaluation of the safety is obtained by transforming the complete system error model into the input for a standard quantitative evaluation tool [51], and the safety analysis process follows a standard approach as shown in Figure 2.16. Problems caused by malicious attacks are not addressed by HARA within the ISO 26262 standard, although such attacks may

SAFURE D2.2 Page 16 of 144

pre-empt a safety strategy.

Figure 2.16: Overview of the safety analysis process ([51]).

The STRIDE threat model provides a way to methodically review system designs and highlight security design flaws. The proposed SAHARA (Security-Aware Hazard Analysis and Risk Assessment) method allows the evaluation of the impact of security issues on safety at the system level. In the same work, threats are quantified with reference to the ASIL analysis, according to the Resources and Know-How that are required to define threats and the Threats Criticality, see Figure 2.17. The impact of the threat on the system determines whether the threat is safety-related or not. If the threat is safety-related, it will be analyzed and the resulting hazards will be evaluated. The Common Criteria (CC) standard [50] was developed to facilitate the security evaluation of information technology products. This standard provides a common set of requirements for measuring the assurance of a product during a security evaluation. In particular, the CC addresses the protection from three main security aspects: unauthorised disclosure, modification, or loss of use.

| Level | Required Resource                           | Example                                                        |

|-------|---------------------------------------------|----------------------------------------------------------------|

| 0     | no additional tool or<br>everyday commodity | randomly using the user inter-<br>face, strip fuse, key, coin, |

| 1     | standard tool                               | screwdriver, multi-meter, multi-tool                           |

| 2     | simple tool                                 | corrugated-head screwdriver,<br>CAN sniffer, oscilloscope      |

| 3     | advanced tools                              | debugger, flashing tools, bus<br>communication simulators      |

| Level | Required Know-How                          | Example                                                                             |

|-------|--------------------------------------------|-------------------------------------------------------------------------------------|

| 0     | no prior knowledge<br>(black-box approach) | average driver, unknown in-<br>ternals                                              |

| 1     | technical knowledge<br>(gray-box approach) | electrician, mechanic, basic<br>understanding of internals                          |

| 2     | domain knowledge<br>(white-box approach)   | person with technical train-<br>ing and focused interests, in-<br>ternals disclosed |

| Level | Threat Criticality                                | Example                                                                                       |

|-------|---------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 0     | no security impact                                | no security relevant impact                                                                   |

| 1     | moderate security relevance                       | annoying manipulation, partial reduced availability of service                                |

| 2     | high security relevance                           | damage of goods, invoice ma-<br>nipulation, non-availability of<br>service, privacy intrusion |

| 3     | high security and<br>possible safety<br>relevance | maximum security impact and life-threatening abuse possible                                   |

Figure 2.17: SAHARA method: Required Resources, Know-How and Threat Criticality ([104]).

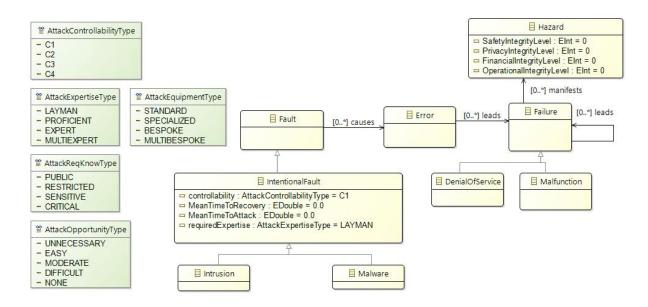

In the EVITA Project [64], parameters for the risk analysis are determined using attack trees. The root of an attack tree is an abstract attack goal and its children represent possible attack objectives that could satisfy the attack goal. Attack objectives are decomposed into a number of attack methods and an attack method is

SAFURE D2.2 Page 17 of 144

further decomposed into a logical combination (AND/OR) of attacks against one or more assets. The attack method with the highest attack probability can be identified and specific countermeasures can be applied to reduce the risk level. For safety-related security risks, the risk level is determined by a combination of the following measures:

- Severity,

- Attack probability and

- Controllability (potential for the human response to influence the severity of the attack).

The classification of Severity separates different aspects of the consequences of security threats: operational (interference with functions that are not safety-related), safety (interference with safety-related functions), privacy (driver privacy or reputation for manufactures) and financial (financial losses). These components may have different ratings from 0 to 4, as shown in Figure 2.18.

| Security                   | Aspects of security threats                                                                                   |                                                                                                   |                                                             |                                                                                         |

|----------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| threat sever-<br>ity class | Safety (S <sub>S</sub> )                                                                                      | Privacy (S <sub>p</sub> )                                                                         | Financial (S <sub>F</sub> )                                 | Operational (S <sub>o</sub> )                                                           |

| 0                          | No injuries.                                                                                                  | No unauthorized access to data.                                                                   | No financial loss.                                          | No impact on operational performance.                                                   |

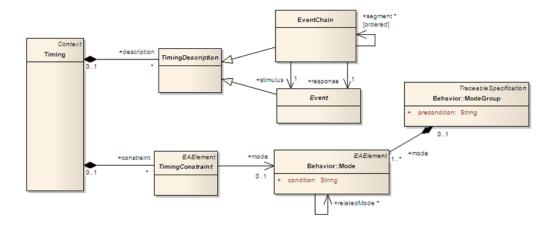

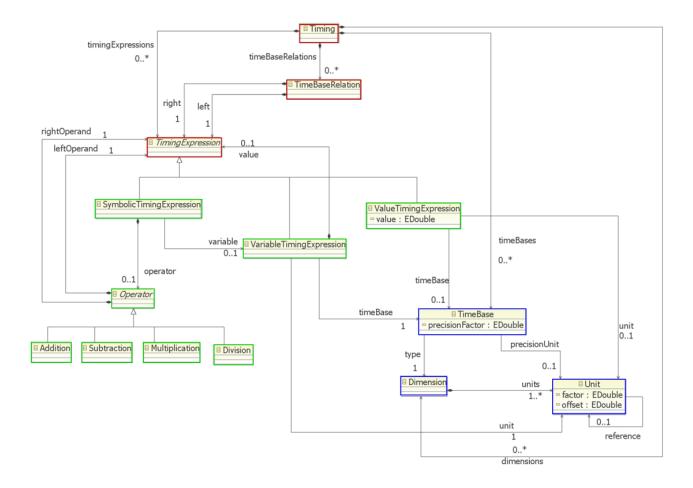

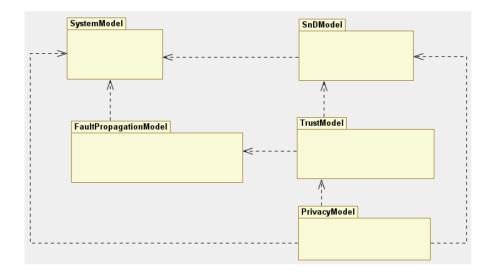

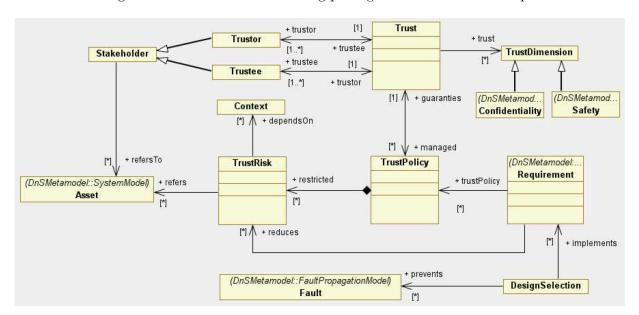

| 1                          | Light or moderate injuries.                                                                                   | Anonymous data only<br>(no specific driver of<br>vehicle data).                                   | Low-level loss (~€10).                                      | Impact not discerni-<br>ble to driver.                                                  |